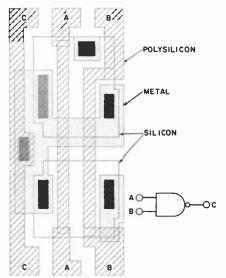

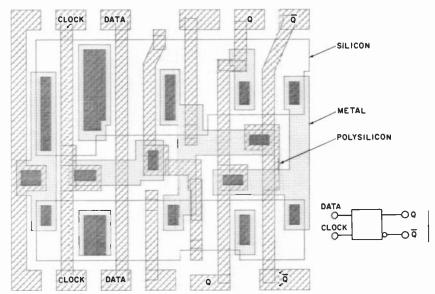

Roger Stewart at the Solid State Technology Center (SSTC) gave us a black-and-white scanning electron photomicrograph of a CMOS/SOS buried-contact memory cell. Our printer added color via a special posterization process. Then we superimposed photographs showing the design, fabrication, testing and application aspects of large scale integration (LSI) for this special issue.

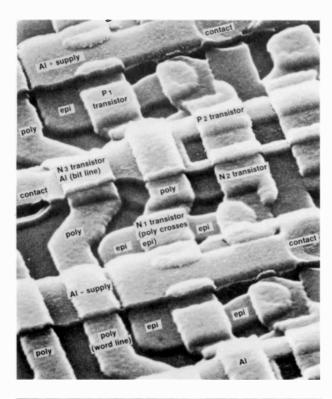

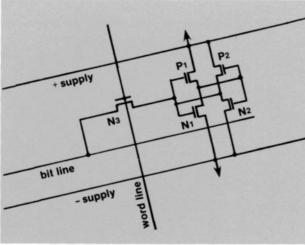

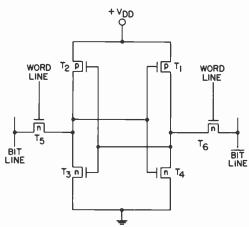

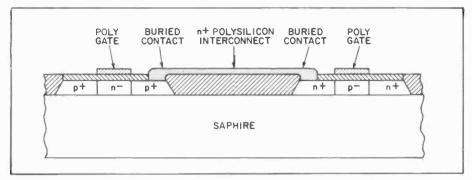

We've printed the original photograph, labeled it, and put Roger's schematic diagram below it so that you can see the five cross-coupled transistors forming the memory cell. There are three layers of material. The epitaxial silicon (epi) layer is the base layer, the polysilicon (poly) forms "word lines" that run top to bottom in the photo in the middle layer and the aluminum metal lines, "the bit lines," run diagonally on the top layer. Poly crosses epi where the transistors are located.

Good CMOS technology efficiently interconnects the three layers of material. Before, CMOS makers painstakingly interconnected all layers to metal. Today at RCA, with the help of Andy Dingwall (see article with Roger Stricker, p. 71) and other SSTC and division researchers, poly and epi in buried contact with each other form an efficient subterranean connection.

## RGA Engineer

A technical journal published by RCA Research and Engineering Blda. 204-2

Cherry Hill, NJ 08358

TACNET: 222-4254 (609-338-4254)

#### **RCA Engineer Staff**

Tom King Editor

Mike Sweeny Associate Editor

Louise Carr Art Editor

Frank Strobl Contributing Editor

**Betty Gutchigian** Composition **Dorothy Berry Editorial Secretary**

#### **Editoriai Advisory Board**

Pete Bingham Division Vice-President, Engineering,

Consumer Electronics Division

Jay Brandinger Division Vice-President, "SelectaVision"

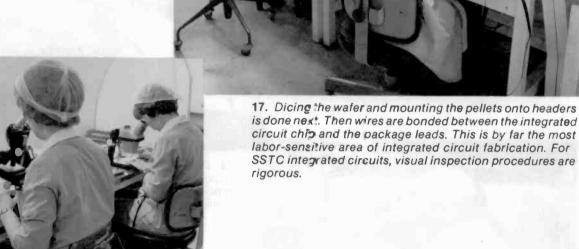

VideoDisc Operations

John Christopher Vice-President, Technical Operations,

**RCA Americom**

Division Vice-President, Engineering, **Bill Hartzell**

Picture Tube Division

Jim Hepburn Vice-President, Advanced Programs,

**RCA Globcom**

Hans Jenny Manager, Engineering Information **Arch Luther**

Division Vice-President, Engineering, **Commercial Communications**

**Systems Division**

**Howie Rosenthal** Staff Vice-President, Engineering

**Ed Troy** Director, Operations Planning and

Support, Solid State Division

**Bill Underwood** Director, Engineering

**Professional Programs**

Joe Volpe Director, Product Operations,

Missile and Surface Radar

**Bill Webster** Vice-President, Laboratories

#### **Consulting Editors**

**Ed Burke** Administrator, Marketing

Information and Communications,

Government Systems Division

Walt Dennen Director, Public Affairs,

John Phillips

Solid State Division

Charlie Foster Manager, Systems and Procedures

Manager, Proposals and Publicity,

**Automated Systems**

To disseminate to RCA engineers technical information of professional value To publish in an appropriate manner important technical developments at RCA, and the role of the engineer. • To serve as a medium of interchange of technical information between various groups at RCA . To create a community of engineering interest within the company by stressing the interrelated nature of all technical contributions. To help publicize engineering achievements in a manner that will promote the interests and reputation of RCA in the engineering field. • To provide a convenient means by which the RCA engineer may review his professional work before associates and engineering management. • To announce outstanding and unusual achievements of RCA engineers in a manner most likely to enhance their prestige and professional status.

Henry Kressel

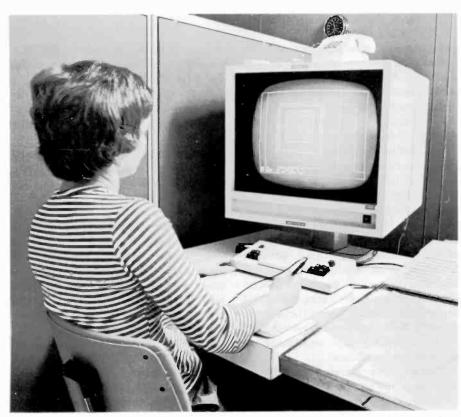

#### Human resources interconnect for VLSI

The economic power of nations used to be measured by steel production or shipbuilding. Now we are entering an age when microelectronics — wafer fabrication and chipbuilding — will become an important gauge of national technological competence. Microelectronics has reached center stage in corporate and national economic planning because complex integrated circuits form the heart of electronic systems.

Microelectronics success requires silicon — the most common raw material, and the dedicated efforts of very skillful teams of specialists in materials, computer science and electronic design — the scarcest resource. RCA has its share of the scarce human resources vital to success in microelectronics, and a distinguished record of innovation. RCA's management is dedicated to increasing our microelectronic ability both for the marketplace and for our internal needs.

The eighties will be the decade of circuitry featuring very large scale integration (VLSI) with more than 100,000 metal-oxide semiconductor (MOS) transistors per chip. The timely realization of such complex devices requires a highly-disciplined team effort that addresses, starting in the early developmental stages, issues of design, manufacture, reliability and testing. The production of these VLSI devices with micron-sized features will require increasingly complex equipment, computer-aided design and our understanding of physical and chemical phenomena that, before now, were inconsequential in integrated circuit fabrication. This issue of the *RCA Engineer* presents subjects ranging from the advanced process technology plans for the SSTC to the applications of custom integrated circuits to communications systems, broadcast equipment and consumer electronic products.

The successful manufacturers of VLSI devices will have masterfully managed the efforts of many specialists to achieve closely defined goals. The chain of interlocking skills will begin in the research laboratory, extend into the factory and end with the successful VLSI system performance. Working closely with the Solid State Division and other users, the David Sarnoff Research Center in Princeton, and the Solid State Technology Center (SSTC) in Somerville will continue to play vital roles in expanding RCA's solid state abilities.

Henry Kressel

Staff Vice-President

Solid State Technology

**RCA Laboratories**

### Highlights

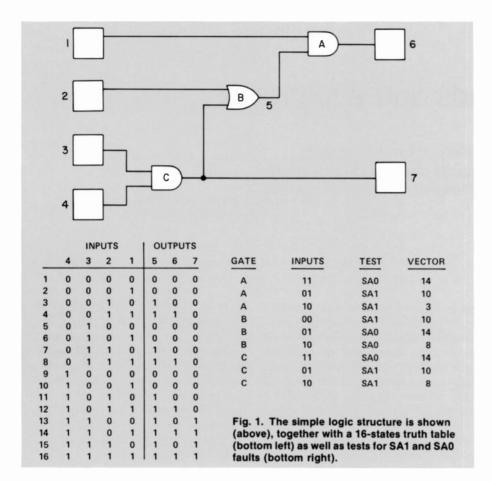

| TEST | VECTOR |

|------|--------|

| SA0  | 14     |

| SA1  | 10     |

| SA1  | 3      |

#### in this issue...

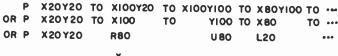

Fabrication technologies include improved photolithographic and etching techniques for ICs with two-tothree micron gate-lengths; process techniques and improved cleanliness to reduce defects in the dielectric and interconnect layers on IC chips; and computer-aided, ultraprecise, closed-loop manufacturing systems for wafer processing. See articles on pages 4, 8, 18, 24, 29.

Computer-aided design and testing tools must keep up with the growth in IC complexity and the demands for: system, logic, circuit and process design; physical implementation (layout); test generation (fault coverage) and test data analysis; and verification/simulation at all levels. More importantly, the new tools and approaches must be practical enough to be accepted and used routinely. See articles on pages 33, 42, 46, 53.

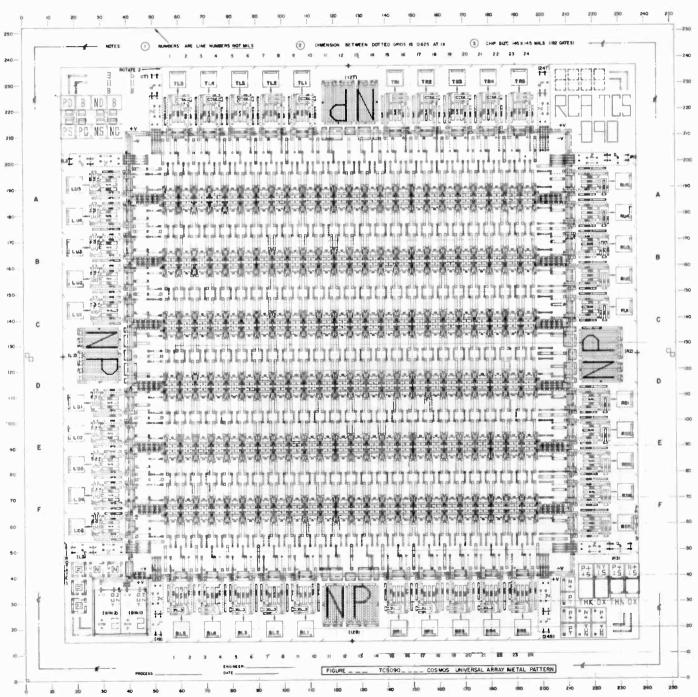

Applications for the new LSI and VLSI technologies in this issue include 72 CMOS gate-universal-array applications implemented by nine different RCA division-locations; the Government Communications Systems' TENLEY/SEELEY program applications; CMOS random-access memories (RAMs); and more. See articles on pages 58, 64, 71.

#### In future issues...

communications trends, mechanical engineering, human aspects of engineering, computer-aided design and manufacturing.

# Vol. 26|No. 2 Sept.|Oct. 80

| overview                             | 4  | VLSI dimensions, designs and decisions  1. Kalish                                                          |

|--------------------------------------|----|------------------------------------------------------------------------------------------------------------|

| fabrication technologies             | 8  | Advanced process technology at the Solid State Technology Center E.C. Douglas                              |

|                                      | 18 | What electron-beams can do for LSI<br>R.A. Geshner                                                         |

|                                      | 24 | The road to LSI: a photographic journey w.A. Bosenberg                                                     |

|                                      | 29 | Computer-aided wafer processing R. McFarlane                                                               |

| computer-aided design<br>and testing | 33 | The evolution of design automation toward VLSI  L.M. Rosenberg                                             |

|                                      | 42 | A system for the automated design of complex integrated circuits A.E. $Heath R.P.$ Lydick                  |

|                                      | 46 | A multi-technology checking program for large-scale integrated circuits B.S. Wagner                        |

|                                      | 53 | LSI testing methods and equipment R.H. Bergman T.R. Mayhew                                                 |

| applications                         | 58 | The gate-universal-array for digital CMOS G. Skorup                                                        |

|                                      | 64 | Custom LSI: an effective tool for digital communications equipment E.J. Mozzi C.A. Schmidt                 |

|                                      | 71 | Advances in CMOS static memory development R.E. Stricker A.G.F. Dingwall                                   |

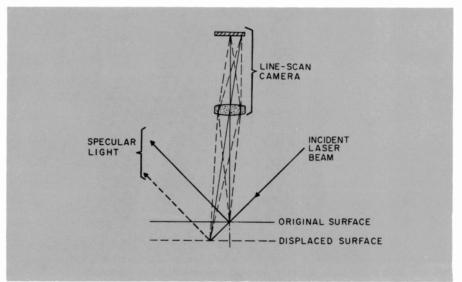

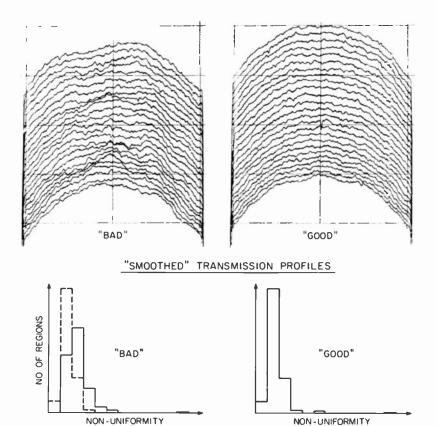

| general interest                     | 75 | Electro-optical techniques for measurement and inspection D.P. Bortfeld I. Gorog P.D. Southgate J.P. Beltz |

| departments                          | 81 | Patents                                                                                                    |

|                                      | 82 | Pen and Podium                                                                                             |

|                                      | 83 | News and Highlights                                                                                        |

# VLSI dimensions, designs and decisions

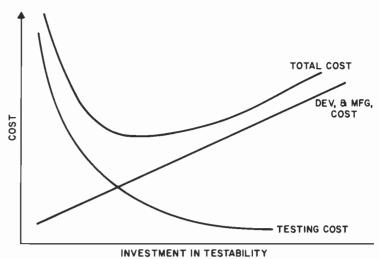

VLSI circuits designed without error and fabricated without flaw pose tough technical problems, but the decisions and cost-considerations that go into VLSI implementation in real electronic systems may be the hardest ones of all.

Abstract: VLSI memory development has meant new fabrication and design problems but, for the most part, VLSI fabrication is upon us. The extreme complexity of VLSI circuitry poses design, simulation and testing problems but computer-aided design has attacked these problems. The hard decisions are between catalog parts and custom designs, between NMOS and CMOS technology.

Twenty years of vigorous innovation, creative exploitation of the laws of nature and man's tools have carried semiconductor technology from the excitement of a single resistor-transistor logic (RTL) gate in a package to the routine expectation of 100,000-gate complexes. This transition signals the advent of VLSI, Very Large Scale Integration.

#### VLSI dimensions

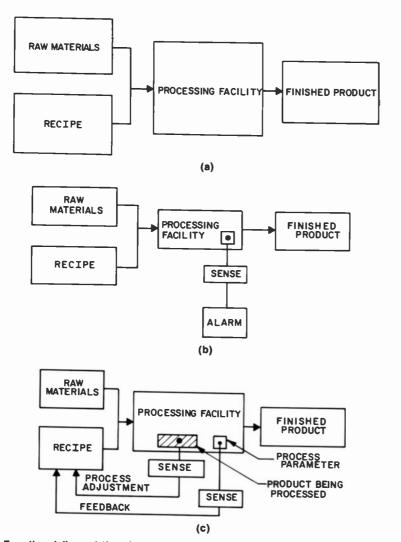

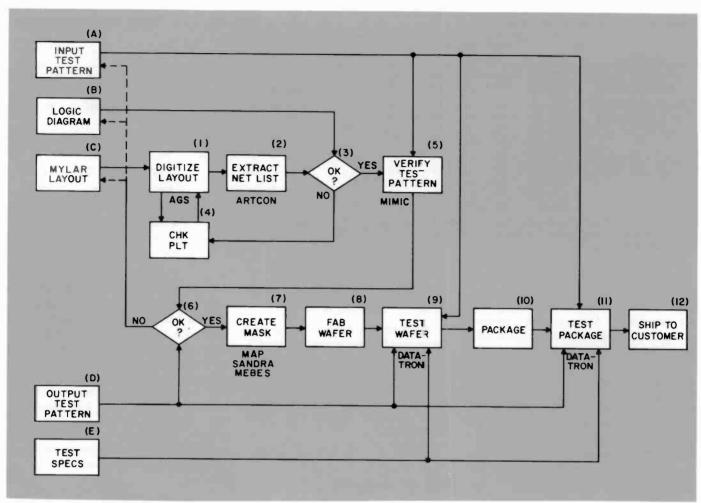

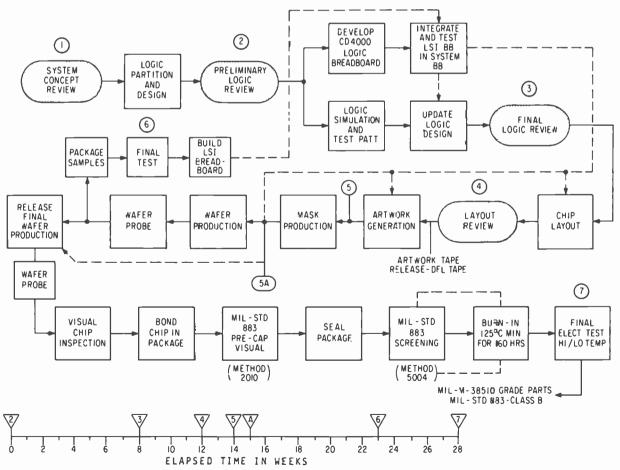

The development of fabrication methods to make hundreds of thousands of components per package has meant more than just supplying systems designers with more functions at lower cost. It has drastically altered the strategy and the timing of the semiconductor product generation cycle. Figure 1 summarizes the traditional steps leading to a semiconductor product.

Engineers use the electrical needs of a system to define the product. In the design phase, they generate a schematic and make a layout to establish the masks needed for fabrication. If evaluation confirms that the design meets system goals, the device can proceed into production. If the evaluation reveals design shortcomings, then that phase of the cycle is repeated.

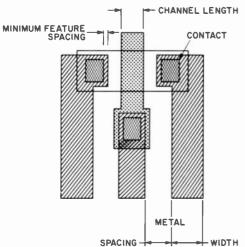

To develop simple semiconductor functional electronic blocks, engineers worked to define and refine the fabrication phase. They optimized technology to achieve the highest device performance consistent with practical manufacturing yields. Usually the definition, design and evaluation phases would take less than one year of engineering effort. VLSI has altered the effort allocation drastically. With the exception of memory development - and that exception is a major one — the developers of a VLSI circuit must assume that no new technology needs to be developed for its fabrication. It presupposes that a technology exists, usually as a result of a memory development effort, capable of fabricating and interconnecting thousands of components simultaneously. That technology is defined in terms of processing schedules for the factory and in terms of design rules for the designer. Table I lists some important design rules associated with MOS technologies. Their significance in determining the minimum device structure is illustrated in Fig. 2.

The design rules, together with modeling

PRODUCT DEFINITION

DESIGN

FABRICATION

EVALUATION

PRODUCTION

Fig. 1. Steps leading to a semiconductor product.

equations, provide the circuit designer with the transconductances, resistances and capacitances associated with the chosen

Table I. VLSI design rules.

|                         | 1980      | 1985      |

|-------------------------|-----------|-----------|

| Channel length          | 2-5μm     | 1-2μm     |

| Minimum contact         | 4μm x 4μm | 2μm x 2μm |

| Metal width and spacing | 10μm      | 6μm       |

| Minimum feature spacing | lμm       | .5μm      |

Reprint RE-26-2-1 Final manuscript received August 12, 1980.

Fig. 2. Significance of VLSI design rules in determining minimum device structure.

technology and, therefore, permit the valid prediction of both circuit performance and chip size. Thus, the following problems remain: given 100,000 transistors of known electrical ability, how can we apply and interconnect all transistors to achieve a desired system function, and how can we verify, through appropriate testing, that the complex arrays will function satisfactorily even under worst-case conditions of both system-environment and processrelated parametric variations? The successful solutions to these problems can require ten-to-twenty engineering years and a real-time expenditure of one-to-three years. The availability of human technical resources is the major problem limiting the growth of VLSI technology.

#### VLSI designs

Unlike other forms of VLSI, the development of semiconductor memories has meant the development of new technology. System requirements for semiconductor memories have been clearly defined more, More, MORE! The acronyms have evolved from PMOS to NMOS to highdensity NMOS to SOS and the features have diminished from mils to microns in response to a still insatiable demand for more bits-per-package. A specific memory design's universal applications and highvolume use have justified mammoth investments for engineering and for capital to the needed fabrication establish technology.

In the last five years, memory-cell sizes have shrunk from five square-mils-per-bit to less than one square-mil-per-bit, making 64K memories commercially feasible. A combination of circuit design, advanced

technology and innovative device structures has increased this functional density. For example, dynamic memories offer the functional density greatest capacitors store the information, thus making one-transistor memory cells possible. But customers need memories that can retain information indefinitely, so circuitry was developed to refresh (replace) the charge that tends to leak away. In addition, circuit advances in the sense amplifiers of memory circuits permitted the detection of extremely small packets of charge, making it possible to use minimum-sized storage capacitors. Clearly, advanced technology - mask-making, photolithographic resolution improvements and anisotropic plasma-etching techniques has reduced minimum feature sizes.

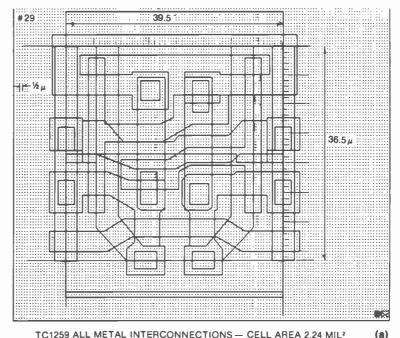

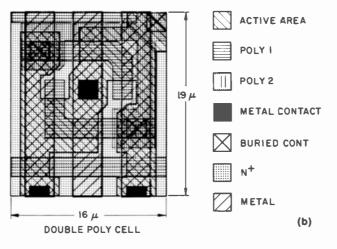

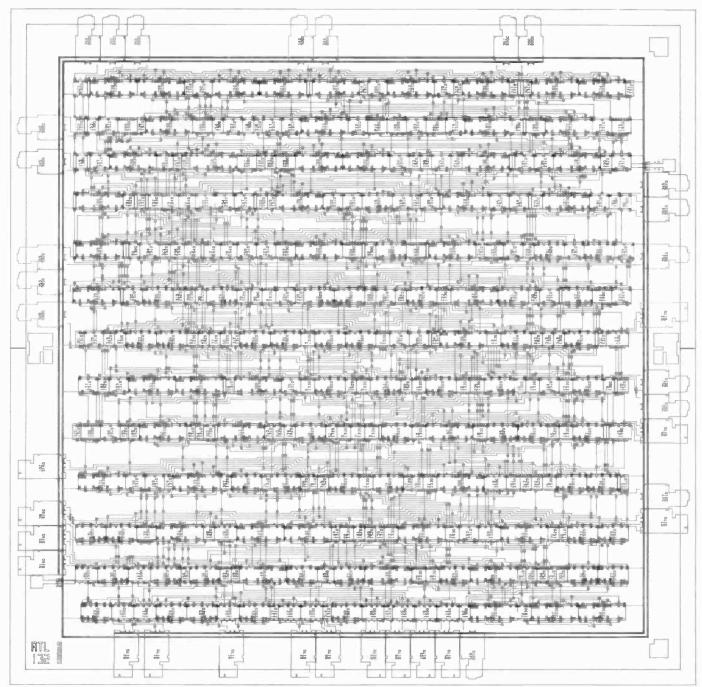

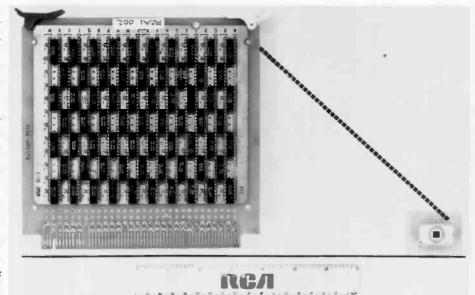

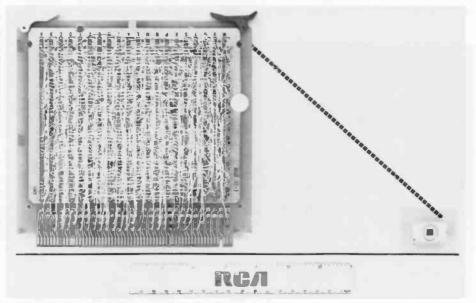

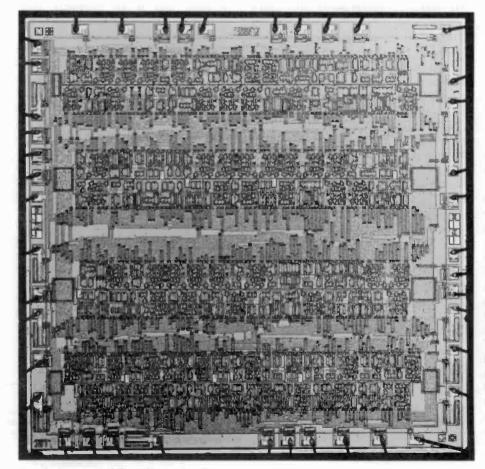

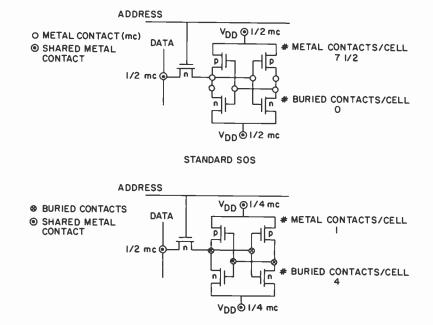

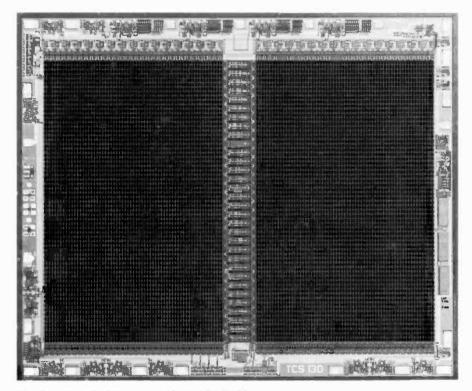

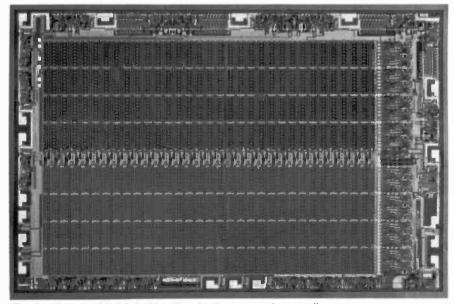

Figure 3 shows how innovative device structures improve density. Both structures exemplify arrays of static memory cells

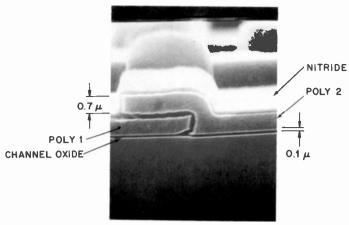

designed using the limits of RCA's developmental three-micron CMOS II technology. The cells in Fig. 3a use a straightforward isoplanar silicon-gate CMOS technology and, because of the advanced design rules of the CMOS II technology, can be as dense as two squaremils-per-bit. The cells in Fig. 3b, in addition to exploiting advanced design rules, assume the increased process complexity of a two-level polysilicon process that can be used to achieve more efficient circuit crossovers and smaller load elements. This design approach results in a density of 0.6 square-mil-per-bit, a density compatible with the practical production of a 64K static memory. Figure 4, a scanning electron photomicrograph of a multiple polysilicon structure, illustrates vertical as well as horizontal structures in device design.

VLSI exploits technologies developed

TC1259 ALL METAL INTERCONNECTIONS — CELL AREA 2.24 MIL<sup>2</sup>

Fig. 3. Arrays of static memory cells designed RCA's developmental three-micron CMOS II technology.

Fig. 4. SEM of multiple polysilicon structure.

for high density memories to achieve complex logic functions. Also, as mentioned earlier, the design and evaluation phases demand a major engineering effort. Human talent for creative genius often is accompanied by human fraility and the potential for error. So, even a massive investment of talent in a complex microprocessor program would not guarantee success in a reasonable amount of time. This problem has been attacked through the innovative development of a number of programs for computer-aided design (CAD). These programs permit the designer to calculate the performance of a given schematic in terms of a potential technology, to validate an approach to implementing a given logic function, to define the topological interconnections needed to achieve a function using standard logic blocks, to generate the photomask patterns needed for device fabrication, and to define, automatically, test routines that will evaluate the finished devices. Table II describes some of the CAD programs now actively used by RCA LSI and VLSI designers.

#### VLSI decisions

Assuming that VLSI circuits can be designed without error, then fabricated without flaw, we will consider other aspects of VLSI implementation in a real electronic system. For example, should we use a standard catalog part or a custom design? The advantages of a custom part include the potential for a minimum parts count, a possible proprietary advantage in the use of an exceptionally high-performance design approach, and unique systeminterface requirements. The advantages of catalog parts include lower cost, more predictable delivery, an established reliability history and more fully

Table II. CAD programs for LSI and VLSI

| Program name | Function                                                                          |  |  |

|--------------|-----------------------------------------------------------------------------------|--|--|

| R-CAP        | Circuit simulation program                                                        |  |  |

| LOGSIM       | Logic simulation Time-based (gate delays)                                         |  |  |

| TESTGEN      | Logic simulation Worst cast hazard analysis                                       |  |  |

| ART          | Mask artwork manipulation                                                         |  |  |

| CRITIC       | Design-rule checking                                                              |  |  |

| APAR         | Automatic placement and routing programs MP2D, PP2D                               |  |  |

| AUTOROM      | Automatic generation of pattern-generator and test programs from bit-pattern file |  |  |

characterized designs. The disadvantages of custom designs include higher cost because the parts are usually made in lower volume, unreliable delivery because the design and evaluation cycles are unpredictable, and an increased probability that unanticipated bugs will be discovered during system prove-out. VLSI catalog functions include random access memories (RAMs), read only memories (ROMs) and

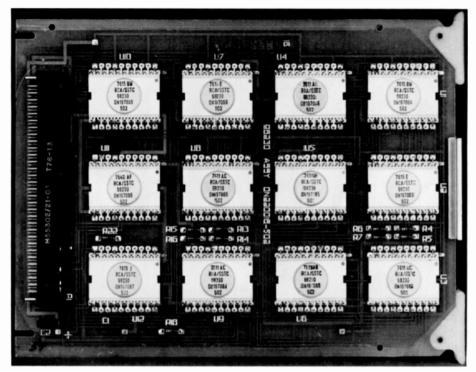

microprocessors. Except in high volume applications such as automotive electronics, custom designs of such parts are rarely justified. Where LSI or VLSI custom parts are justified, different approaches can be taken to minimize risks. One of these approaches is the use of universal arrays.

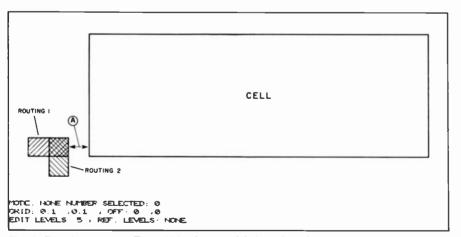

A universal array is a circuit consisting of a matrix of identical logic elements, such

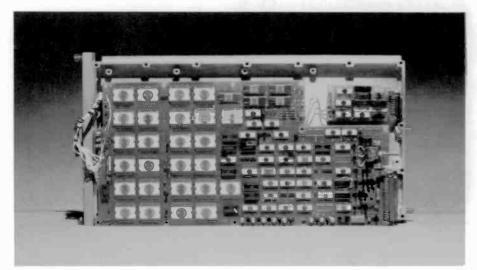

Fig. 5. Closed-cell logic (C<sup>2</sup>L) circui: used to implement the PRIMUS color weather radar display program.

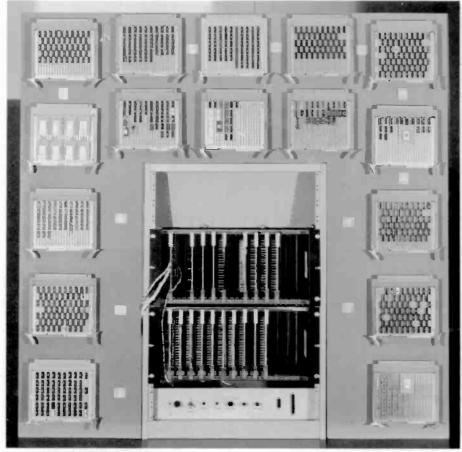

as gates. We can use the same array to implement many logic functions simply by modifying one mask level - the metallization used to interconnect the elements. This significantly reduces the engineering design time and, because the basic circuit elements have been proved out in other configurations, assures that the design will perform as predicted. The disadvantages of the universal-array approach are poor packing density and, because device geometries cannot be customized, less than the maximum speed inherent in a given technology. Where reduced package count is a primary system goal, however, the universal-array approach has been used very effectively. Figure 5 is a photograph of one of the closed-cell logic (C2L) circuits used by RCA's Van Nuys Avionics Division to implement its successful PRIMUS color weather radar display program.

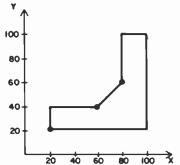

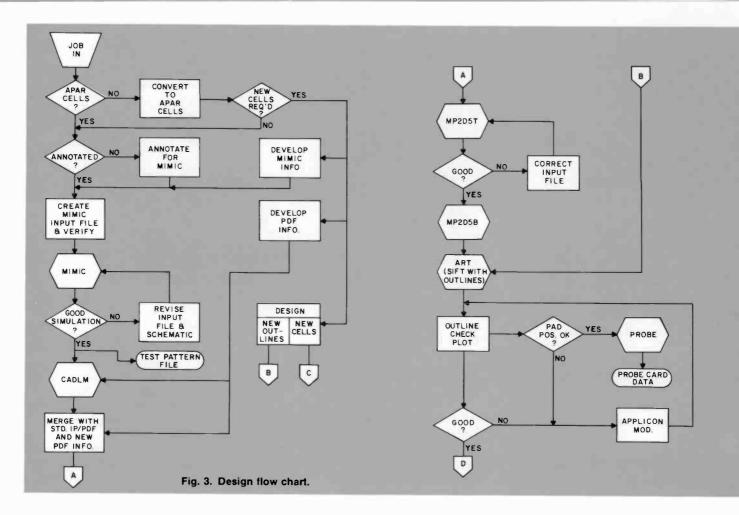

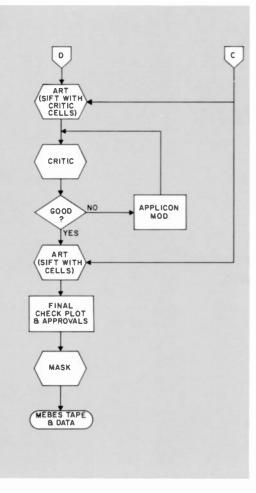

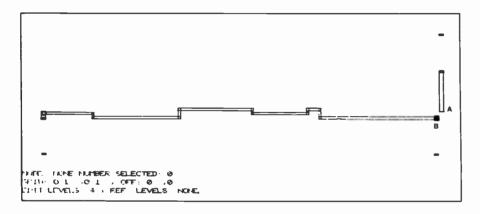

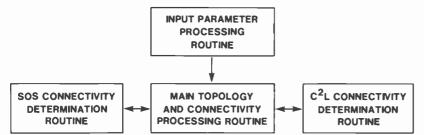

Figure 6 illustrates an automatic standard cell layout program that minimizes the need for design engineering. This approach, APAR (automatic placement and routing), also uses standardized building blocks to accomplish complex logic. Instead of the handful of different elements available in the universal-array approach, hundreds of different building blocks are available. These blocks are not located in prediffused positions on a silicon wafer. They are software definitions in a computer memory. A computer program is used to transform the logical requirements of a function into an array of optimally chosen and optimally interconnected elements.

A disadvantage of the APAR approach is that new masks have to be generated for all processing levels. This increases initial engineering costs and processing time, but these increases represent only a small part of the total design cycle and are usually justified by the increased density and performance of APAR designs. Figure 6 illustrates the application of APAR to implement a general processing unit function using SOS technology. Clearly, the APAR packing density is an improvement over the universal-array packing density. The large percentage of chip area devoted to metal interconnections is particularly significant. The number of components on a memory-structure chip is primarily limited by the size of the elements. In contrast, VLSI areas are limited by inefficient interconnections between random logic elements.

System requirements and costconsiderations primarily determine the technology chosen for VLSI. Most industry LSI approaches exploit the high

Fig. 6. The APAR circuit-design approach uses standardized building blocks to accomplish complex logic.

density and performance of the dynamic NMOS approach for most applications, and use bipolar technologies where maximum speed is crucial. CMOS approaches excel where power, noise margin and ambient operating ranges are more important. The high component count of VLSI makes power a primary consideration because capacitively dissipated power will significantly limit the density advantage of dynamic NMOS approaches. The bipolar speed advantage is being eroded increasingly by the performance of shortchannel (one-to-three microns) MOS structures. For these reasons, a highdensity version of the CMOS technology that exploits short-channel, isoplanar and multiple-level interconnection options will emerge as the mainstream VLSI technology.

Iz Kalish has been involved in the design and development of semiconductor devices since joining RCA in 1953. He is presently Manager of the IC Design and Process Development group of the Solid State Technology Center where he is responsible for the development of the next generation of VLSI technology needed to implement high performance memories and microprocessors in both bipolar and field effect devices. Iz has authored several papers on semiconductor devices and a book, Microminiature Electronics.

Contact him at: IC Design and Process Development Solid State Technology Center Somerville, N.J. **TACNET: 325-6243**

# Advanced process technology at the Solid State Technology Center

Teams at the Solid State Technology Center are exploring formable tools and process innovations to fabricate the next generation of high-density complementary metal-oxide semiconductor circuits.

Abstract: The component density of metal-oxide-semiconductor integrated circuits (MOS IC) has been increasing rapidly in recent years and these trends toward larger circuit complexity and smaller individual component size have required a continuous refinement and advancement of process technology. This paper describes how RCA's Solid State Technology Center (SSTC) is meeting the challenge of very large scale integrated (VLSI) circuits with development programs in key technology areas.

## The challenge of high-density technology

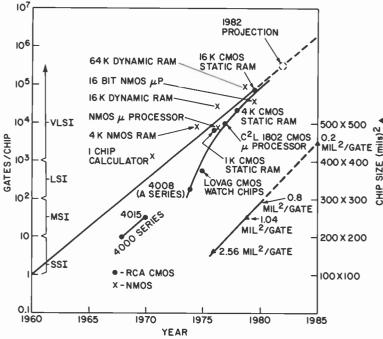

The metal-oxide-semiconductor integrated circuit (MOS IC) industry has been characterized by an extremely rapid growth from medium scale integration (MSI) in 1965, (10<sup>1</sup> to 10<sup>2</sup> gates per chip) to very large scale integration (VLSI) manufacturable today, (10<sup>4</sup> to 10<sup>5</sup> gates per chip). Figure 1 shows the trend of this growth in gate complexity for both RCA's CMOS technology<sup>1</sup> and the NMOS technology<sup>2</sup> that is popularly used by other MOS IC manufacturers. Figure 1 also

shows the actual and the projected growths of MOS IC die size<sup>2</sup>. These trends toward larger circuit complexity and smaller individual component size have required a continuous refinement and advancement of process technology in order to maintain high yields and to achieve manufacturing

cost effectiveness. If these trends are to continue at the pace projected in Fig. 1, then the challenge to be met is the development of advanced process technology which can produce larger sizes of defectless chips and, at the same time, can achieve smaller feature sizes within the chip.

Fig. 1. Both the size and the density of integrated circuit chips has been increasing rapidly with time.

Reprint RE-26-2-2 Final manuscript received June 18, 1980.

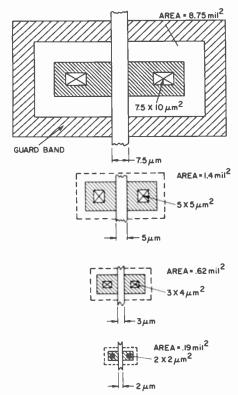

A graphic illustration of the nature of this challenge is shown in Fig. 2 where the geometric structure of bulk transistors of gate lengths running from 7.5 to  $2\mu m$  are shown. In order to keep up with the projected growth, photolithographic techniques and etching techniques which can controllably pattern 3µm and 2µm gate length structures must now be in the development stage. Since chip area is expected to increase by a factor of ~4 by 1985, process techniques must now be in the development stage which reduce the number of defects in the various dielectric and interconnect layers on the chips. In addition, increased cleanliness is required, both in layer-formation techniques and in the overall operation of the fabrication facility.

RCA's Solid State Technology Center is meeting the VLSI challenge on a broad front. Working on some projects in close cooperation with the Research Laboratories in both Princeton and Zurich, major process development programs are presently being pursued in the following areas:

- · Fine-line photolithography

- Low-pressure chemical-vapor deposition (LPCVD)

Fig. 2. A graphic illustration of the decrease in the area required for a bulk transistor as the gate length is decreased.

Table I. Characteristics of contact and projection systems.

| Technique                                    | Minimum<br>feature size<br>(µm) | Source wavelength (Å) | Overlay tolerance<br>(µm) | Major limitations                                     |

|----------------------------------------------|---------------------------------|-----------------------|---------------------------|-------------------------------------------------------|

| Contact                                      | Submicron                       | Hg                    | 0.5-0.75                  | defects, runout, mask cost, linewidth variation       |

| Proximity                                    | 3-4                             | Hg<br>Xe              | 0.5-0.75                  | minimum geometry, defects linewidth control           |

| Projection                                   |                                 |                       |                           |                                                       |

| 1:1                                          | 2-3                             | Hg                    | 0.5-0.75                  | minimum geometry                                      |

| 1:1 (deep<br>UV)                             | ~0.5                            | 2400                  | ?                         | source, optics, resist availability                   |

| Direct step<br>on wafer<br>(DSW)             | 1.25-1.8                        | 4040                  | 0.125-0.35                | accommodation of wafer distortion                     |

| X-ray                                        | ~0.3                            | 4-8                   | ?                         | source complexity,<br>mask structure,<br>registration |

| Electron<br>beam<br>direct write<br>on wafer | 0.1-0.2                         | _                     | 0.1-0.3                   | cost, throughput                                      |

- Direct digital control of thermal oxidation and diffusion

- · Plasma etching

- Silicide metallization

- Upgrading of white room fabrication facility

In the following sections, the activities in each of these areas will be described and will be related to the overall SSTC goal of developing advanced processing for larger area, higher density integrated circuits.

#### Fine-line photolithography

As the density of integrated circuits increases, limits are placed on both the

minimum feature size that can be photoprinted and the control which can be achieved in the photoprinting process. Table 13 summarizes the characteristics and major limitations of the photoprinting techniques which are presently being investigated by the IC industry. Proximity printing, 1:1 projecting printing, and direct-step-on wafer techniques are actively being studied at SSTC. In addition to using various types of photoprinters, automatic equipment is being used to coat wafers with photoresist and to develop the exposed wafer, thereby achieving a high degree of control and reproducibility in the chemical processing of photoresist.

Table I shows that although contact

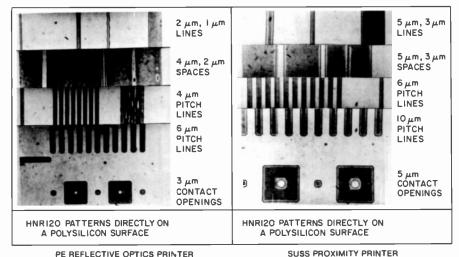

Fig. 3. Performance of various photo-printers. The dimensions given are those on the mask which was used to print the pattern. Each set of patterns was made with the same exposure, i.e., each set comes from the same wafer.

printing is capable of replicating submicron feature sizes, contact printing is unsuitable for VLSI applications because of the defects which are caused on both the photomask and the wafer by the contact process, and because of the runout which is caused by wafer/mask distortion when they are clamped together. For these reasons, even older, less demanding integrated circuit production is being shifted to the contactless proximity and imageprojection techniques.

#### Proximity printing

A simple method of achieving contactless photoprinting is to space the mask a small distance from the wafer (2.5 to  $25\mu$ m) and project a "shadow" of the mask onto the photoresist-coated wafer. This proximity-printing technique costs much less than image-projection systems since no lens is involved. The technique also has the flexibility of allowing the use of a wider range of illumination wavelengths which, like contact printing, is limited essentially only by mask transmissivity.

SSTC is experimenting with a Suss Model 55 Proximity Printer<sup>4</sup> and has found that feature sizes in the 3 to  $5\mu$ m range can be printed under optimum conditions (Fig. 3). Since a proximity printer uses the diffraction-dominated shadow of a mask, the resulting exposed image (for the case of negative resist) is a trade-off between complete exposure, minimum resist-loss during development, and minimum "orange peel" on the one hand, and line-width deterioration and resist bridging on the other hand. Proximity

printing also leaves noticeably rounded corners, and the nature of the surface underlying the photoresist can affect the exposed image. Polysilicon is the most difficult surface on which to pattern. The use of a broad-band, high-pressure, flashed-Xenon light source can minimize some of these problems by allowing a polychromatic printing-characteristic.

#### Reflective image projection

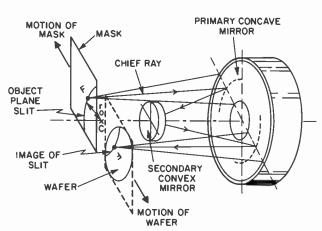

Image-projection techniques can improve the quality and control of contactless wafer-exposure. Early attempts in this direction used large-field, refractive lenses but were generally unsuccessful because of problems with lens aberrations, light scattering, temperature stability, telecentricity, focal depth and field coverage. Simply stated, it is hard to grind glass lens elements that can produce 3- to 4-inch diameter images with 1-to-2µm resolution. An alternate approach is to use reflective optics5, and in addition to combine reflective optics with the scanning concept which reduces the complexity of the reflecting surface needed to cover a large field. The Perkin-Elmer 120 and 220 projection aligners used in SSTC are based on the scanning, reflective-optical principle which is diagrammed in Fig. 4.

Even though the accurately formed optical surfaces in a scanning reflective

system are fewer in number and smaller in size when compared with the refractive system counterpart, the physical fabrication of a focusing mirror and its optical coating is still the limiting factor in 1:1 reflective-projection system. Improved measurement techniques, using a laser, allow the presently obtainable rms tolerances of finished optical surfaces to approach  $\lambda/100$ . This is sufficient to allow the printing of feature sizes in the 2-to-3 $\mu$ m range (Fig. 3).

#### Direct-step-on-wafer techniques

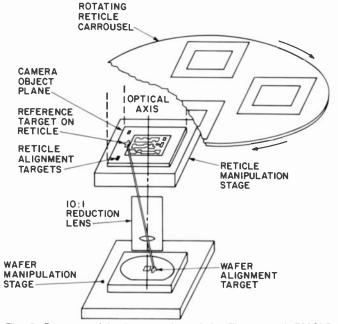

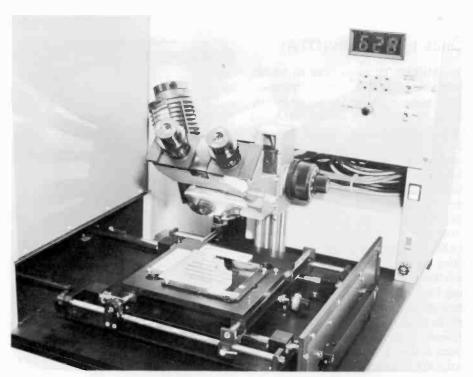

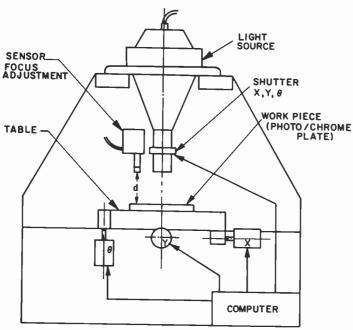

Direct-step-on-wafer (DSW) machines provide the printing technique with the optimum combination of minimum feature size and overlay tolerance<sup>3,6</sup>. This is achieved by using a 10:1 refractive projection system which employs a 10X reticle, projects and exposes an individual chipsize image on the wafer, and step-andrepeat-prints the number of chips needed to cover the wafer surface. Since the field size of a 10:1 reduction lens is relatively small, ~10mm (~400 mils) in diameter. stepper lenses can be fabricated to give  $\sim 1 \mu m$  resolution capability. Figure 5 illustrates the operation of the Electromask 700SLR wafer stepper presently being used at SSTC.

The difficulties associated with a DSW machine are not in the lens. Positioning the

Fig. 4. Diagram of basic 1:1 reflective optical system which images a ring field (circular object plane slit) using a primary concave mirror and a secondary convex mirror. As shown, the mask and wafer must be translated in opposite directions at the same rate. In a real system, such as the Perkin Elmer (PE) 120 or 220, the optical path is bent with additional prisms so that both the mask and the wafer can be mounted on the same translating carriage.

Fig. 5. Diagram of basic operation of the Electromask 700SLR Direct Step-on-Water 10:1 projection aligner. The machine is capable of automatic reticle changing, through the lens alignment, and  $\pm 0.25 \,\mu$ m alignment tolerance.

wafer accurately during the stepping procedure, aligning the printing of each stepped exposure, and obtaining fast enough stepping operation in order to achieve a reasonable throughput are the difficulties. Positioning accuracy is achieved with a laser-interferometrically controlled air-bearing x-y table which is computer controlled and is capable of positioning accuracies within  $\pm 0.25 \mu m$ . Alignment accuracy is achieved using a TV-based through-the-lens microscope system which aligns the 10X reticle directly to the wafer (Fig. 5). With only two alignments - one on each side of the wafer — the Electromask system is capable of overlay printing individual chips across the surface of a 3-inch wafer with  $\pm 0.25 \mu m$ overlay tolerance. Although the SSTC Electromask machine is not yet equipped with automatic alignment at each chip position, Electromask has developed such a system that can be retrofitted to the SSTC machine. All this automatic performance, however, makes it difficult to achieve high wafer throughput. With optimized printing of the largest available field and two automatic reticle changes per level of printing, the throughput of the Electromask machine will be between 30 and 50 wafers per hour.

## Low-pressure chemical-vapor deposition — the quest for fewer defects

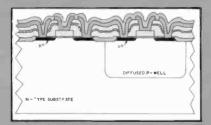

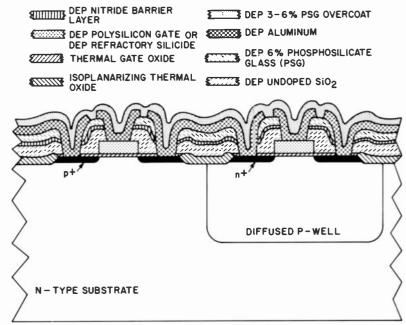

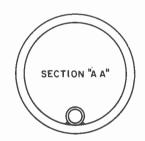

MOS ICs are fabricated by the systematic formation and patterning of layer upon layer of dielectric or interconnect materials. Figure 6 shows a diagram of such a layered structure which forms a complementary pair of bulk CMOS transistors (actual ICs may not use all of the layers shown). Of the eight layers used to fabricate the structure, six of them are deposited layers. For reliability and high yield, all eight layers should be perfectly uniform, with no included defects, and should contain no unwanted contaminants. In addition, as is evident from Fig. 6, the layers should conformally cover the various topological steps which result in the structure because of the patterning.

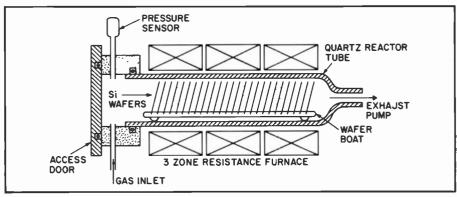

Until recently, the techniques used to deposit these layers have involved chemical-vapor deposition at atmospheric pressure which is in general plagued with problems of uniformity control and particulate formation<sup>7</sup>. The development of commercially available reactors for chemically depositing the required layers at

much-reduced pressures (~0.5 torr) has helped to overcome these problems, and LPCVD reactors have already supplanted other techniques for forming silicon nitride (Si<sub>3</sub>N<sub>4</sub>) and undoped polysilicon layers. Work is presently underway at SSTC to

establish LPCVD techniques for depositing both doped and undoped silicon dioxide (SiO<sub>2</sub>) layers and for depositing doped polysilicon.

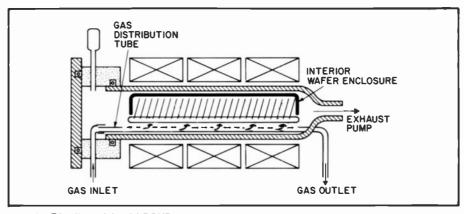

Two variants of the basic tubular LPCVD reactor are available, as shown in

Fig. 6. Diagram of a layered structure forming a bulk CMOS complementary pair of transistors.

Fig. 7a. End-feed LPCVD reactor.

Fig. 7b. Distributed-feed LPCVD reactor.

Table II. Deposition processes available in commercial LPCVD reactors.

| Layer                                                | Input gases                                                         | Deposition<br>Temperature<br>(°C) | Deposition rate** (Å/Min) | Reactor type |

|------------------------------------------------------|---------------------------------------------------------------------|-----------------------------------|---------------------------|--------------|

| Undoped SiO <sub>2</sub>                             | SiH <sub>4</sub> ,O <sub>2</sub> ,N <sub>2</sub>                    | 400-430                           | 100                       | Distributed  |

| Doped SiO <sub>2</sub><br>(PSG)                      | SiH <sub>4</sub> ,PH <sub>3</sub> ,O <sub>2</sub> ,N <sub>2</sub>   | 400-430                           | 90-110                    | Distributed  |

| Undoped<br>Polysilicon                               | SiH <sub>4</sub> ,N <sub>2</sub>                                    | 610-640                           | 100-125                   | End feed     |

| Doped*<br>Polysilicon                                | SiH <sub>4</sub> ,N <sub>2</sub> ,PH <sub>3</sub>                   | 730                               | 200                       | Distributed  |

| Silicon Nitride<br>(Si <sub>3</sub> N <sub>4</sub> ) | SiH <sub>2</sub> Cl <sub>2</sub><br>NH <sub>3</sub> ,N <sub>2</sub> | 740-800                           | 40-65                     | End feed     |

| High temperature<br>Undoped SiO <sub>2</sub>         | $SiH_2Cl_2, N_2, N_2O$                                              | 960                               | 120                       | End feed     |

<sup>\*24</sup> ohm/square layers, 3200Å thick, post-annealed for 30 min at 1000°C.

Fig. 7. Either type of reactor can handle typically ~100 wafers per pump-down. The "end-feed" reactor shown in Fig. 7a was developed first and is used predominantly at higher deposition temperatures. Chemical vapor deposition processes are surface-catalyzed reactions, and if the reaction rate at the optimum deposition

temperature is small compared to the mass transfer rate (the rate at which gas can be pumped through the tube), then the deposition process will be uniform because the density of active gaseous species is uniform, that is, the active species is not significantly depleted along the length of the tube. The optimum reaction conditions depend on temperature; Table 11 shows the conditions presently considered optimum for forming uniform layers of polysilicon, SiO<sub>2</sub>, and Si<sub>3</sub>N<sub>4</sub> using the end-feed reactor.

At temperatures lower than 950°C for the case of SiO<sub>2</sub> depositions (and at temperatures higher than 700°C in the case of undoped polysilicon), the pump rate cannot conveniently be made high enough to raise the mass-transfer rate above the reaction rate. Thus, in an end-feed reactor, non-uniform depositions occur both over the surface of a given wafer and as a function of the position of the wafer in the tube. This problem can be solved using the distributed-gas system shown in Fig. 7b and by using an enclosure inside the reactor which surrounds the wafers. Two parallel tubes run the length of the reactor, one carrying silane (SiH4) and the other carrying oxygen (O2) when SiO2 is being deposited. These gases are injected into the interior wafer-enclosure uniformly along the length of the tube. Using this technique, the reacting species have a smaller distance to diffuse in order to reach all areas of all the wafers in the tube, hence significant active-species depletion is

Fig. 8. Diagram of the electronic feedback systems used in a direct digital control (DDC) oxidation/diffusion furnace (Courtesy Thermco).

<sup>\*\*</sup>The exhaust pump rate in all cases is 35-40 cfm.

reduced over the region of a given wafer and hence deposition uniformity is increased. Layers of doped and undoped oxide having a ±5 percent variation can be achieved in the 400-500°C temperature range using the distributed-feed technique.

In those cases where depositions must be made in the 300-400°C temperature range, plasma-enhanced LPCVD can be used<sup>8</sup>. The use of a plasma to achieve chemical activation of layer deposition has the advantage of producing low-temperature films having good conformal coverage. A disadvantage of the technique is the odd stoichiometry that can result. Instead of the desired Si<sub>3</sub>N<sub>4</sub>, for example, one usually obtains Si<sub>x</sub>N<sub>y</sub>H<sub>z</sub> or Si<sub>x</sub>N<sub>y</sub>H<sub>z</sub>O<sub>w</sub>.

Because of the large number of wafers typically  $\sim 100$  — which can be uniformly deposited on in a single run, and because of the low-pressure operation, which uses much smaller amounts of reaction gas than reactors which operate at atmospheric pressure, LPCVD-deposition techniques are inherently more economical. Also, at the low pressures used, gas-phase nucleation is far less and hence particulate formation from this source is negligible. Deposition does occur on the reactor walls and on the wafer boat, but if the tube and boat are cleaned every 20th run in the case of undoped polysilicon when using a  $\sim 0.6 \mu m$ deposition thickness per run, flaking is not a problem. The deposits on the hot tube walls are glassy and adherent, and any particles that may form have only a small chance of falling on the vertically-oriented wafers. With good uniformity and low layer defect potential, as well as the good conformal-coating properties, LPCVD is a natural for LSI applications.

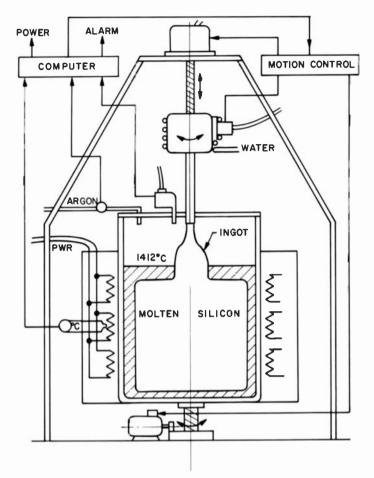

## Direct digital control of oxidation and diffusion

Although only two of the eight layers diagrammed in Fig. 6 are formed by thermal oxidation, significant oxidation, diffusion and annealing steps are required in the LSI fabrication sequence. The latter processing steps require that the wafers be inserted into and removed from hightemperature furnaces generally ranging in temperature from 800 to 1200°C. Besides the desired effects of oxide growth or dopant diffusion, this large thermal cycling of the wafers causes many undesirable side effects. These undesirable effects include the introduction of wafer-slip<sup>10</sup> due to insertion and/or removal from the furnaces at too rapid a rate, the introduction of oxidation-induced stacking faults<sup>11</sup> if improper pre-oxidation or post-oxidation ambients are used, or the precipitation of bulk-oxygen cluster-defects if incorrect post-processing anneals <sup>12, 13</sup> are used. These undesirable effects lead to MOS yield loss due to high leakages and individual transistor failure.

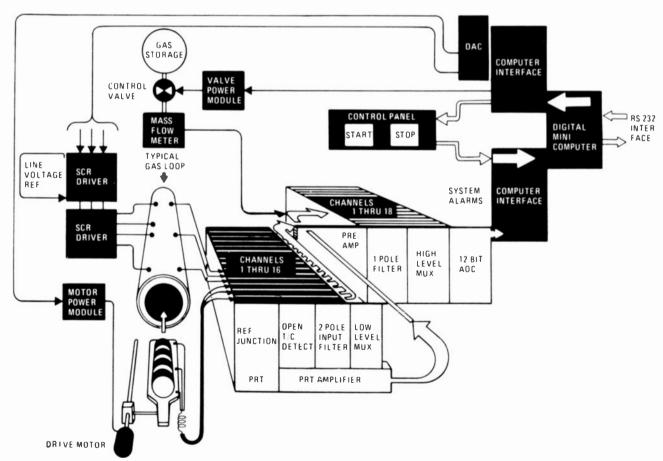

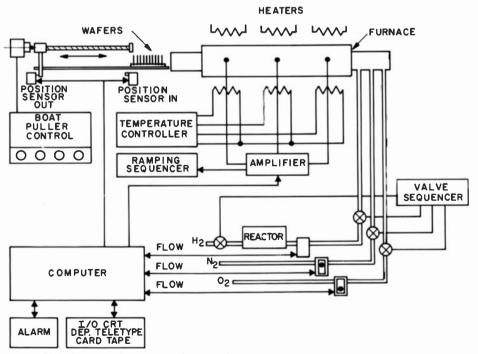

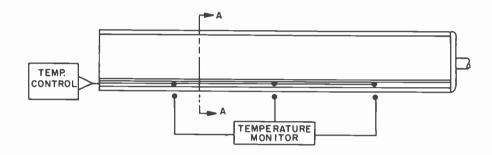

Greater control over the thermal processing of wafers can be obtained by using direct digitally controlled furnaces. A diagram of such a furnace system is shown in Fig. 8. The heart of the system is a microprocessor which organizes the overall furnace processing using feedback control loops. These control loops are used to insert and withdraw the wafer paddles at a specified rate, to raise or lower the furnace temperature at specified rates, to adjust the various gas flows as a function of time, and to monitor the actual temperature profile inside the furnace as a function of time. The microprocessor can, in addition, automatically clean the furnaces (using hydrochloric acid (HCl) or trichloroethane (TCA), perform an automatic calibration cycle and tailor the dynamic performance of the furnace to a given process step by appropriately adjusting the proportional band-control constants. Since these various furnace operations are specified in terms of a software instruction sequence,

DDC furnaces provide a high degree of process reproducibility. All of these features can, of course, be achieved without digital control. But with digital control they can all be easily achieved at the same time. A disadvantage of digital control is that all control is lost if the computer system fails.

SSTC presently has 16 DDC 4-inch diameter tube furnaces and is actively developing LSI processing using their capabilities.

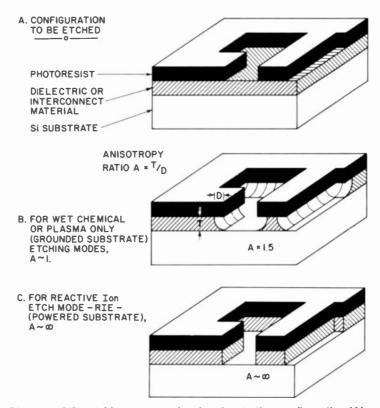

## Plasma etching — transferring dimension accurately from mask to wafer

After fine-line photolithographic techniques have been used to define an etch mask (Fig. 9a), the next step is to etch the underlying dielectric or interconnect material with dimensional control. Plasma etching, or alternatively dry plasma-processing or dry etching, is a developing technology which promises to be critically important to the fabrication of high-density integrated circuits. Successful fabrication of high-density LSI requires etch control of fine lines. This etch control becomes difficult or impossible for wet chemical etching if the width of the line to

Fig. 9. Diagram of the etching process showing the starting configuration (A), and results when isotropic etching (A =  $T/D\simeq i$ ) is used (B) or when anisotropic (C) etching (A $\sim \infty$ ) is used.

Fig. 10. Four different variations of piasma-etcher configurations.

be controlled approaches the thickness of geometry and source-gas mixtures, a specthe layer being etched. This difficulty is trum of controllable etching characteristics caused by the isotropic nature (Fig. 9b) of can be achieved which ranges from most wet chemical reactions and by the isotropic to highly anisotropic (Fig. 9c). surface-tension effects associated with This combination of features has caused fluid flow which prevents the etchant and the present intense interest in the developthe reaction products from freely exchangment of dry-processing techniques for ing in confined surface topologies. high-density LSI-circuit fabrication.

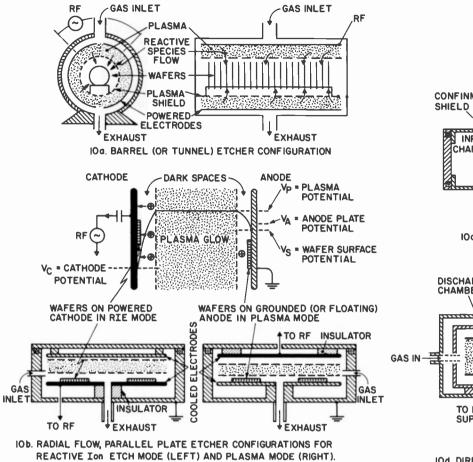

Plasma etching at low pressures overcomes these problems. Plasma processes are used to excite a normally inert gas to a chemically active species, and low-pressure surface-adsorption-desorption reactions—coupled at times with sputtering processes—allow good control of fineline etching. By properly selecting reactor Four different varieties of plasma-etcher configurations (shown schematically in Fig. 10) are presently available for processing IC wafers. The barrel or tunnel reactor is shown in Fig. 10a. For this configuration, the wafers are held in a quartz boat inserted in the central "tunnel" portion of the cylindrical reactor. The plasma is

excited, using an r.f. discharge, in a sheath region which surrounds the tunnel. The chemically active free radicals (i.e., excited neutrals) in the plasma diffuse to the wafers through holes in the central cylindrical plasma shield and react with the wafer surface causing etching through a reduced-pressure adsorption-reaction-desorption process. The etch products are pumped away by the exhaust system. Since no electric field exists in the central tunnel region, no ion bombardment takes place and the surface etching reaction is an isotropic, chemically driven process.

A second configuration, the radial-flow, parallel-plate reactor, is shown in Fig. 10b.

Table IIIa. Plasma generated species interaction with a solid surface.

| Process                  | A                  | В                                     |  |  |

|--------------------------|--------------------|---------------------------------------|--|--|

| Etching species          | lons               | Chemically active neutrals (radicals) |  |  |

| Driving force            | Electric field     | Diffusion                             |  |  |

| Arrival on surface       | Highly directional | Random direction                      |  |  |

| Interaction with surface | Momentum transfer  | Adsorption-reaction-<br>desorption    |  |  |

| Species leaving surface  | Atom clusters      | Gas molecules                         |  |  |

Table IIIb. Processes occurring in various plasma-etch reactors.

| Reactor                        | Process combination                                   |

|--------------------------------|-------------------------------------------------------|

| Barrel                         | В                                                     |

| Parallel-plate RSE or RIE mode | A+B, A>B                                              |

| Parallel-plate plasma          | A+B, B>A                                              |

| Continuous plasma flow         | В                                                     |

| Directed beam                  | A+B+species activation on<br>surface after adsorption |

IOc. EXTERNAL GENERATION, CONTINUOUS FLOW ETCHER CONFIGURATION.

IOd. DIRECTED BEAM ETCHER CONFIGURATION.

For this reactor configuration, the wafers to be etched are placed directly on the system circular-plate electrodes. Since an electric field exists in the vicinity of either electrode (see potential diagram in Fig. 10b), the wafers are not only exposed to the plasma-generated active chemical species, but also are exposed to bombardment sputtering by ions from the plasma. The magnitude of the electric field in front of each plate depends on: the applied voltages; the gas pressure; the plate separation; the secondary emission ratios of the wafers and the electrodes; and the geometric configuration of the reactor, for example the ratio of anode to cathode area14. The magnitude of the electric field in the vicinity of the cathode is generally the largest, and when the wafers are placed on the powered electrode (cathode) and the reactor is operated at low pressures (0.01 -0.05 torr), the bombardment assisted plasma etching is called Reactive Sputter (Ion) Etching (RSE or RIE mode) which yields highly anisotropic etch results 15, 16, 17 Verticle-walled structures (A~∞) have been obtained in SiO2 which have an aspect ratio (height/width) of  $\sim 8^{16}$ .

When the wafers are placed on the anode, where the electric field is smaller, and the reactor is operated at somewhat higher pressure (0.1 - 0.5 torr), chemical processes dominate the etching and the etch results are closer to isotropic etching. By varying the wafer placement, the reactor pressure, or even powering both electrodes, a spectrum of etch characteristic from nearly isotropic (A~1) to nearly anisotropic (A ~∞) can be obtained. Tables IIIa and IIIb summarize the various etch processes. Although exposing the wafer directly to the plasma adds the extra dimension of physical sputtering and enhances the flexibility of parallel-plate etchers, it also introduces the disadvantage of increased radiation damage from the vacuum UV generated in the plasma. This can preclude the use of parallel-plate etchers for the fabrication of rad-hard products.

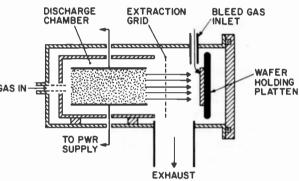

Two variations of the etcher configurations already discussed are shown in Figs. 10c and 10d. In the external generation, continuous-flow configuration, the chemically active species are generated in an external excitation chamber excited by a microwave discharge and then are sprayed onto the wafer surface using a manifold distribution arrangement. The etching properties here are the same as for the barrel reactor (Table IIIb). The directed beam etcher configuration shown in Fig. 10d forms a large-diameter ion

| 3.1-3.3               | .062066                                                                                              |

|-----------------------|------------------------------------------------------------------------------------------------------|

|                       | .002000                                                                                              |

| 3.5-3.6               | .070072                                                                                              |

| 3.6-3.9               | .072078                                                                                              |

| 15-20                 | 0.3-0.4                                                                                              |

| 50-100                | 1-2                                                                                                  |

| 100-150               | 2-3                                                                                                  |

| 800-1000<br>(500-800) | 15-20<br>(10-15)                                                                                     |

| 1750-2250             | 35-45                                                                                                |

| 800-1000              | 16-20                                                                                                |

| 1250-1500             | 25-30                                                                                                |

| 1000-1500             | 20-30                                                                                                |

|                       | 3.6-3.9<br>15-20<br>50-100<br>100-150<br>800-1000<br>(500-800)<br>1750-2250<br>800-1000<br>1250-1500 |

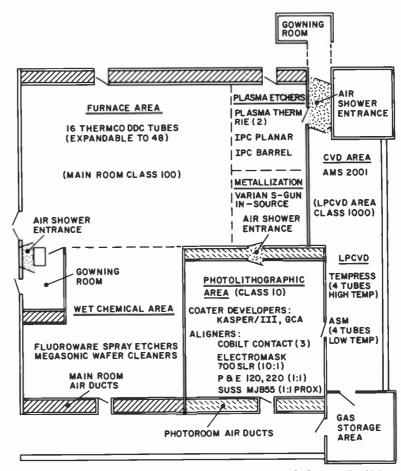

Fig. 11. Diagram of the white room fabrication facility in SSTC, Somerville, N.J.

beam using a discharge chamber and an extraction grid. This technique is similar to the RIE etch mode with the advantage that the ion bombardment energy is easier to control and can be adjusted to any desired value. This extra dimension of control combined with the single-wafer-at-a-time reactor design, can be used, for example, to activate (by bombardment) a species that has been introduced to the wafer surface through a bleed gas inlet and adsorbed onto the surface.

Routine plasma etching of polysilicon in barrel-type etchers using the CF<sub>4</sub>-based chemistry is presently being used at SSTC to fabricate  $5\mu$ m circuits. Active programs, both within SSTC and in cooperation with the Princeton Labs and the Zurich Labs, are underway to develop production-oriented, parallel-plate etchers for anisotropic etching of polysilicon, aluminum, and SiO<sub>2</sub> films.

#### Silicide metallization

As the density of integrated circuits increases, the device lateral dimensions and the layer thickness used must be scaled to smaller values. This includes the conductive interconnect layers of doped polysilicon and aluminum. If the layer conductivities ( $\sigma$ ) or resistivities ( $\eta = 1/\sigma$ ) are not also appropriately scaled, increased interconnect resistance will result which will lead to poor circuit performance. In some chips where circuit speed — low RC values - is critical, such as microprocessor or short-access-time memory chips, overall interconnect resistivity must be reduced even after scaling. As an example, in present memory chips using polysilicon access lines, RC delay accounts for ~5ns of the access time.

Table IV shows the resistivity of various interconnect materials. Polysilicon layers are presently widely used for both selfaligned structures and for structures requiring multilevel interconnects. The resistivities, however, are higher than desired. The low resistivity of aluminum cannot easily be exploited because process temperatures cannot exceed ~450°C after its use. A third class of materials, the refractory metal silicides, have resistivities between aluminum and doped polysilicon. These layers can be formed by alloying sputtered layers of polysilicon and refractory metal, titanium (Ti), tantalum (Ta), tungsten (W) or molybdenum (Mo); by cosputtering the layers, for example, sputtering from a target made of tantalum silicide (TaSi<sub>2</sub>); or by using chemical vapor deposition. RCA is exploring all three techniques at SSTC or at the Princeton Laboratories. Refractory-metal-silicide interconnect layers are targeted for use in the next generation of high-density LSI circuits.

## The upgraded SSTC White Room facility

The successful fabrication of high-density integrated circuits requires, in addition to new processing techniques, a more carefully controlled fabrication environment. The SSTC White Room in Somerville has been renovated extensively to satisfy this environmental requirement. Figure 11 shows a layout of the SSTC White Room along with a listing of the major new pieces of equipment purchased to support the advanced process technology presently being developed.

The room is divided into three areas which are distinguished by the flow rate of the recirculated, filtered air. In all cases, the air is passed through high-efficiency particulate-air (HEPA) filters which remove all particulates over  $0.2\mu m$  in size. Most of the particles larger than this are carried in by personnel, hence the need for dust-confining jumpsuits and air showers at the room entrances. The air-flow rate in the main room is adjusted to 65 linearfeet/min. The main room is Class 100, that is, an environment with a maximum of 100 particles per cubic foot with a size larger than  $0.5\mu m$  and a maximum of 10 particles per cubic foot with a size larger than  $5.0\mu m^{19}$ . In a Class-100 room ~1 particle/cm<sup>2</sup>-hour strikes a given wafer surface<sup>20</sup>. The LPCVD area has a lower flow-rate - 25 linear feet/min - and is rated Class 1000. The photolithographic area, which is rated as Class 10, has its own temperature (70°±2°F) and humidity 37.5±2.5%RH) control and has an air-flow rate of 100 linear feet/min. This flow rate exceeds the ~85 linear-feet/min flow rate threshold for laminar flow, i.e., air flow moving with uniform velocity following essentially parallel flow lines with an absence of eddies. With this type of processing environment, wafer defects caused by dust should be negligible even for large area circuits with feature sizes as small as lum.

#### Conclusions

A number of the new technology areas that are presently being explored at SSTC for

Ed Douglas is Manager, LSI Technology Development in the Solid State Technology Center. He became a Member of Technical Staff at RCA's David Sarnoff Research Center in Princeton, New Jersey, in 1969. He has worked in the area of lensless, highresolution projection techniques. He has worked on the application of ionimplantation techniques to integratedcircuit devices, including the fabrication of high-performance bipolar transistors, the development of implanted P-wells for CMOS structures, and the development of implanted surface guard layers for optimum packing density of CMOS structures. He has worked on the development of lowtemperature, all-implant processes for fabrication of large-array CCD imagers.

Contact him at: Solid State Technology Center RCA Laboratories Somerville, N.J. TACNET: 325-7292

use in fabricating the next generation of high density CMOS integrated circuits have been described. The challenge of VLSI CMOS ICs is a formidable one, but formable tools and a continuous series of process innovations are available to meet this challenge.

#### Acknowledgment

Many helpful discussions were held with W. Bosenberg(Somerville); J. Vossen, N. Goldsmith and W. Kern (Princeton); and H. Lehmann (Zurich). Their help is gratefully acknowledged.

#### References

- Kalish, I.H., "VLSI-Tools, Technology, and Trends," RCA Engineer, Vol. 24, No. 1, pp. 59-61 (June/July 1978).

- Queyssac, D., "Projecting VLSI's Impact on Microprocessors," *IEEE Spectrum*, Vol. 16, No. 5, pp. 38-41 (May 1979).

- Resor, G.L. and Tobey, A.C., "The Role of Direct Step-On-The-Wafer in Microlithography Strategy for the 80s," Solid State Technology, Vol. 22, No. 8, pp. 101-108 (Aug. 1979).

- Snyder, J.R. and Van DeVen, J., "A Better Mousetrap," SPIE, Vol. 174, Developments in Semiconductor Microlithography IV, pp. 75-82 (1979).

- Offner, A., "The Influence of Partial Coherence in the Microprojection of Images," *Proceedings* of the OSA (Jan. 1971).

- Tobey, A.C., "Wafer Stepper Steps Up Yield and Resolution in IC Lithography," *Electronics*, Vol. 52, No. 17, pp. 109-112 (Aug. 16, 1979).

- Kern, W. and R.S. Rosler, "Advances in Deposition Processes for Passivation Films," J. Vac. Sct. Technol., Vol. 14, No. 5, pp. 1082-1099 (Sept./ Oct. 1977)

- Purggraaf, P.S., "Plasma Deposition Trends," Semiconductor International, Vol. 3, No. 3, pp. 23-24 (March 1980).

- Kern, W. and Schnable, G., "Low Pressure Chemical Vapor Deposition for Very Large Scale Integration Processing — A Review," *IEEE Trans. Elec. Devices*, Vol. ED-26, No. 4, pp. 647-657 (Apr. 1979)

- Fisher, A.W. and Schnable, G.L., "Minimizing Process-Induced Slip in Silicon Wafers by Slow Heating and Cooling," J. Electrochem Soc. Vol. 123, No. 3, pp. 434-435 (March 1976).

- Murarka, S.P., Levenstein, H.J., Marcus, R.B. and Wagner, R.S., "Oxidation of Silicon Without the Formation of Stacking Faults," J. Appl. Phys., Vol. 48, No. 9, pp. 4001-4003 (Sept. 1977).

- Helminch, D. and Sirtl, E., "Oxygen in Silicon: A Modern View," Semiconductor Silicon 1977, Huff. H.R. and Sirth, E., Editors, Proceedings, Vol. 77-2, pp. 626-636, The Electrochemical Society, Inc. Princeton, N.J. (1977).

- Sugita, Y., Shimizu, H., Yoshinaka, A. and Aoshima, T., "Shrinkage and Annihilation of Stacking Faults in Silicon," J. Vac. Sci. Technol., Vol. 13, No. 1, pp. 44-46 (Jan./Feb. 1977).

Shimizu, H., Yoshinaka, A. and Sugita, Y., "Formation of Stacking Fault-Free Region in Thermally Oxidized Silicon," Japan. J. Appl. Phys., Vol. 17, No. 5, pp. 767-771 (May 1978).

- Vossen, J., "Plasma Deposition and Etching Reactors for Semiconductor Applications,"

Proceedings. 4th Intl. Symposium on Plasma Chemistry, Vepruk and Hertz, J., Editors.

- International Union of Pure and Applied Chemistry, Vol. 3, p. 344-345 (1979).

- Lehmann, H.W. and Widmer, R., "Fabrication of Deep Square Wave Structures with Micron Dimensions by Reactive Sputter Etching," App. Phys. Lett., Vol. 32, No. 3, pp. 163-165 (Feb. 1978)

- Lehmann, H.W. and Widmer, R., "Profile Control by Reactive Sputter Etching." J. Vac. Sci. Technol., Vol. 15, No. 2, pp. 319-326 (March, Apr. 1978)

- Knopp, K., Lehmann, H.W. and Widmer, R., "Microfabrication and Evaluation of Diffractive Optical Filters Prepared by Reactive Sputter Etching," J. Appl. Phys., Vol. 50, No. 6, pp. 3841-3848 (June 1979).

- 18. Table Obtained from H. Lehmann, RCA Zurich Laboratories

- U.S. Federal Standard 207B, GSA Business Service Center, New York, N.Y.

- Lounsbury, J.B. and Klein, K.I., "Limitations in Photolithographic Semiconductor Processing," Electronic Packaging and Production (March 1974)

## New Publication from the RCA Engineer

According to the RCA Engineering Information Survey conducted in 1977, RCA Engineering is the second most important source of technical information about RCA, (the most important information source being the engineer's associates). The back issues of the Engineer — 150 of them — provide a record of RCA's progress in invention, development, and manufacturing. To make this wealth of technical information accessible to the engineer, a 25-Year Index to RCA Engineer has been published.

The Index can help you find specific information that is needed in your work. Or the Index might provide a vital contact in another RCA business who has related experience and who would be willing to consult with you. The Index gives you the opportunity to profit from RCA's technical heritage—to reuse knowledge, to build on past accomplishments.

The 25-Year Index to RCA Engineer is available in all RCA Libraries.

Recipients of the RCA Engineer can obtain their personal copies by writing to:

RCA Engineer Building 204-2 Cherry Hill, NJ 08358 As chip size gets larger and more complex and line-size gets smaller and more sensitive to lithographic defects, the design engineers and manufacturing process engineers need to know.....

## What electron-beams can do for LSI

Abstract: The manufacturing electronbeam exposure system is a microlithography photomask-making system that can delineate, for today's LSI masks, extremely fine lines in complex geometrical configurations on electronsensitive resist polymer. The author also reviews a constellation of related technologies.

#### LSI designer problems

In 1950, a digital gate cost \$10, was made with vacuum tubes and covered 2500mm<sup>2</sup>. Today, a digital gate costs 1 cent and is contained within only .001mm<sup>2</sup>. Today's design engineer must cope with everincreasing design complexity on semiconductor chips that are becoming larger.

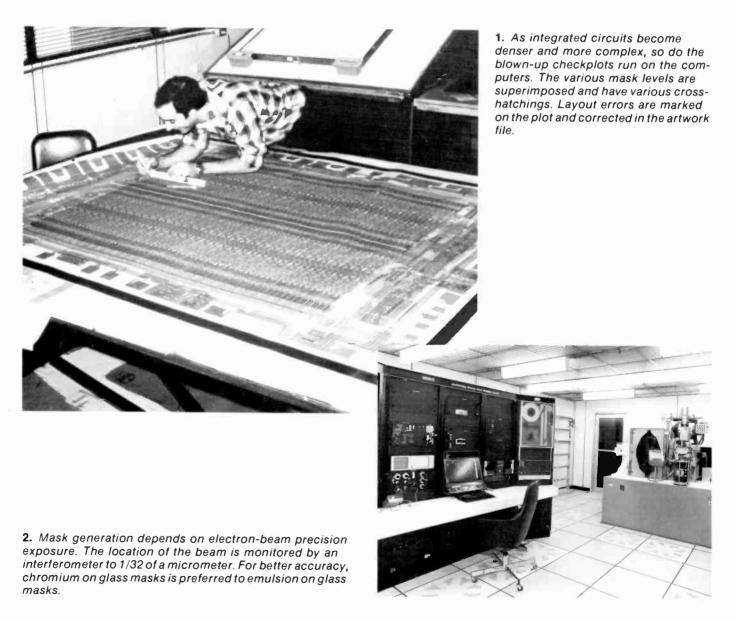

Devices (basic functional cells) and their line sizes are becoming smaller. Design density will continue increasing at the rate of 60 percent each year. With just this increase in complexity, the design engineer would be "pulling out his hair" if he didn't have a complete computer-aided design (CAD) system that allows computerized preparation of his design information with almost immediate translation to hard mask tools.

As an example, with smaller line sizes, the tolerance on transistor source-to-drain spacing gets smaller. This means line-size tolerances must get smaller to allow these devices to realize required performance gain and to stay within operating parameter specifications. Additionally, as the chip size gets larger there are

Reprint RE-26-2-3 Final manuscript received May 29, 1980. fewer chips on the wafer, which means registration of each process mask step is more critical. These factors and defect density factors introduced during wafer processing take their toll in yield, raising the price of the semiconductor device. We need a lithography system that will keep the yield high, and also economically will make larger, more densely packaged circuits.

Typically, the design engineers must also prove out their design through an actual sample design-verification production run. They must produce a complete mask set and make wafers. In today's dynamic semiconductor industry, these designverification runs have to be completed in record time. The design must be proven quickly to get the product into large-scale production and on the market if we are to realize an effective return on investment. It must be possible to modify the design and get masks quickly. The refined design must be documented and cast in concrete for production runs. Correct designs must be immediately reproducible from day to day to maintain production. The computeraided-design, 1X mask production system developed around the manufacturing electron-beam exposure system (MEBES) helps the designer to accomplish these functions. Conventional masks are thin pieces of clear glass with an even thinner coating of opaque chromium in which the desired circuit configuration is delineated for a particular step in the semiconductor manufacturing process. The resolution of the delineated device structures can be no better than the quality of the mask used. In the past, masks were made only by optical microphotographic techniques. Some fundamental limitations in optics can limit our optically making masks for the larger, more complex IC designs. That is why we are in the electron-beam (E-beam) process business today.

## New tools in microlithography

Electron-beam technology for photomask generation has become a viable state-ofthe-art in the last ten years. Several other technologies made this possible including CAD and other electro-mechanicaloptical-chemical techniques such as laser interferometry, cryogenic-ion-pump vacuum systems, scanning electron-beam microscopes (SEMs), air bearings, servopneumatic vibration-isolation mounting, servo-motor control, microprocessors and computers, new polymer resist systems and a lot of ingenuity. We can use this equipment now to shoot a finely focused beam of energized electrons onto an electronsensitive resist polymer. This beam will delineate extremely fine lines in complex geometrical configurations for making high-density, high-complexity large scale integration (LSI) semiconductor devices. RCA has been using a system approach to LSI mask fabrication for about two years.

Electron-beam technology is a complete system approach because it involves: the design engineer who specifies the design data; the CAD procedures and the design captured as a computer-readable representation; the actual lithographic techniques using the E-beam; and the process engineer who uses these new techniques to increase yield.

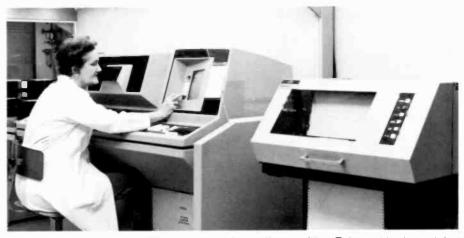

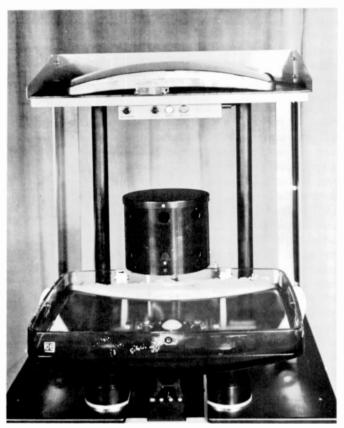

The main advantages of RCA's E-beam technology are that it can make: masks up to 5-inch x 5-inch over a 4.1-inch drawn field; line sizes down to  $0.5 \,\mu\text{m} \pm 0.1 \,\mu\text{m}$ ; masks with defect densities of <1 defect/inch2; complete mask sets from CAD tape to first contact prints in less than three days in more than 50 percent of the cases; and the most complex masks on any chip size up to 4-inch x 4-inch. An outline of some of the pertinent E-beam machine specifications is shown in Table I. A picture of SSTC's MEBES equipment is shown in Fig. 1. The specific advantages and disadvantages of E-beam lithography have been reviewed previously in an RCA Engineer article (Vol. 24, No. 3, Oct./Nov. 1978).

#### Manufacturing problems

As designs become more complex and more dense, design rules (the size of the lines and spaces allowed in the design) will become smaller. RCA is actively working with  $5 \,\mu$ m design rules now and is actively moving toward  $3 \,\mu$ m rules. A  $1 \,\mu$ m factory design is technically possible in the future. The use of  $1 \,\mu$ m design rules in the 1980s will have a greater impact on semiconductor technology than any other single factor in the last 20 years. Although MEBES can effectively draw  $1 \,\mu$ m lines from a system standpoint, other problems should be considered.

Let's look at some of the problems that  $1 \mu m$  lines and spaces in LSIs could cause in the immediate future.

- Defects occur in 1X masks and on the wafer. Masks are manufactured and qualified by automatic 100-percent inspection with a 2 μm lower-limit defect-detection system (Fig. 2). If we get to 1 μm lines, on 1X masks, then in all probability at least 0.5 μm defects must be detected. This may be possible but is probably impractical because 0.5 μm detection would be very time-consuming.

- Accuracy in masks, registration, and printing on the wafer must be held to  $<\pm0.25\,\mu\text{m}$ . Today the tolerances on "runout" or variation across the mask are  $>\pm0.5\,\mu\text{m}$ . The wafers vary more than  $\pm0.25\,\mu\text{m}$  during fabrication due to stresses in the wafer caused by uneven topography and high-temperature process steps.

- Metrology problems. If dimensional tolerances must be held to  $\pm 0.25 \, \mu m$ , then the measurement techniques must be repeatable to at least  $\pm 0.025 \, \mu m$  ( $\pm 1 \, \mu$  inch).

- · Mask defect repair could be a problem.

Table I. Typical E-beam machine specifications.

Line-size control

Line definition

Drawing area 4.1 in. x 4.1 in. (5-in. x 5-in. plates)

Table speed 4 cm/s (≈94 in./min)

Interferometer correction resolution 1/32  $\mu$ m ( $\approx$ 1.2  $\mu$ in.) Raster scan 256  $\mu$ m ( $\approx$ 10 mils)

Maximum chip size 16 mm (≈0.63 in.) x 32mm (≈1.3 in.) without special partitioning

Pattern input type Trapezoids

Raster butting error  $\pm 1/8 \mu m$  ( $\approx 5 \mu in.$ )

ter butting error = 1/6 \(\mu\) in (-5 \(\mu\) in ()

Writing address modes 2 (0.5-\mu and 0.25-\mu address)

Pattern resolution in 6000-Å

1 \( \mu\) consistently, 0.25 \( \mu\) m with thinner resist using smallest address

$\pm 0.10 \mu m$

$\pm 1/8 \mu m$  (0.5- $\mu m$  address)

Fig. 1. MEBES mask and reticle drawing facility in a specially controlled clean room environment. The actual drawing equipment is shown on right and the computer console control is shown on left.

Fig. 2. KLA-100 automatic 100 percent mask inspection machine. This machine has a defect detection capability down to 2  $\mu$ m and produces a hard copy map of all defects detected. It is tied directly to a laser chrome defect removal machine (see Fig. 3) and common software and data is shared between equipment.

Fig. 3. A Quantronix laser repair machine used to remove extraneous chrome spot defects on a completed mask. This allows preparation of masks with, in some cases, zero defects/inch².

Today's practice is to use a laser to remove excessive chrome spots and thereby salvage masks with too high a defect density (Fig. 3). The  $1\mu$ m lines will require removal of  $0.25 \mu$ m defects. These defects will be difficult to detect and may be even more difficult to remove when in close proximity to a critical device in a  $1 \mu$ m space.

The problem of testing a chip as complex as a complete computer seems overwhelming.

Yield (the number of good die per wafer) is the bottom line. We have listed a very few obvious manufacturing problems that could affect yield. We need the best systems approach possible to obtain the best yield possible.

## Electron beam systems approach

RCA has a complete systems approach for solving the mask lithography dilemma. The systems approach can handle the design complexity problem for today's 3to-5 µm design rules and can be used for the l μm design rules in the future. We solve today's problems with this systems approach by using 1X contact and 1X projection masks. The MEBES 10X reticle generation and direct-step-on-wafer (DSW) projection equipment can handle future requirements. The keystone of the system is the electron-beam equipment. This system encompasses computer design, magnetic tape transfer, archival storage,

Fig. 4. A schematic of RCA's CAD software system used for developing LSI artwork, analyzing artwork design rule variation, checking artwork and preparing magnetic tape inputs to various pattern drawing equipment including MEBES.

electron-beam mask writing, 100 percent automatic mask inspection and verification. We can adapt the system to all wafer lithography including contact printing, soft or proximity printing, projection printing and direct-step-on-wafer printing. The designer can use CAD to relieve his design complexity problem. The electron-beam gives him the line resolution and the quick turnaround (QTA) he requires, and gives the process engineer the tool-dimensional and defect-density tolerances he requires. This should allow RCA to get the best yield possible.

## Computer-aided design (CAD)

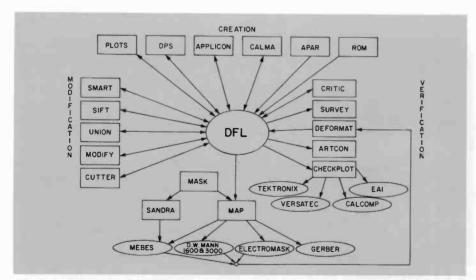

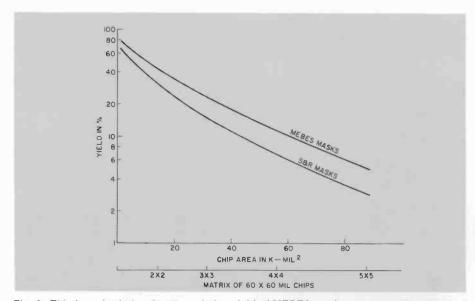

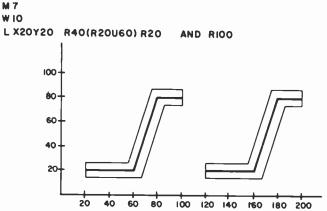

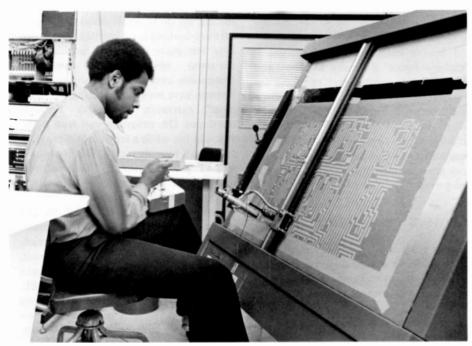

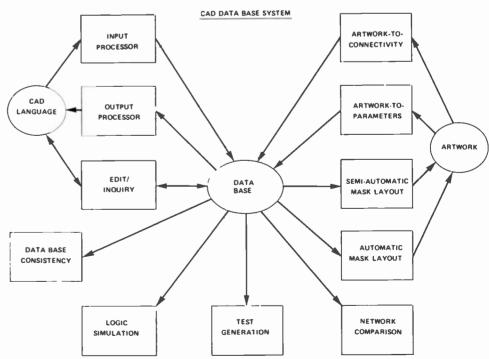

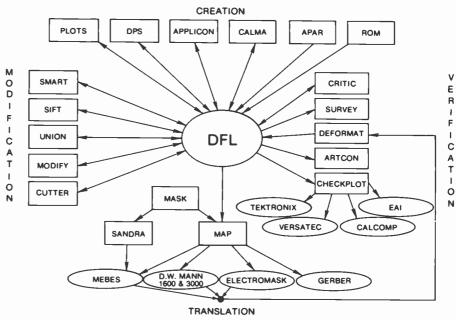

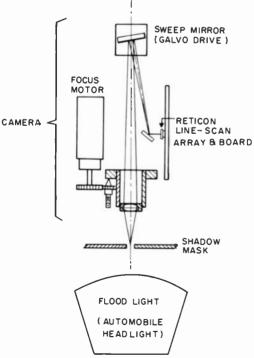

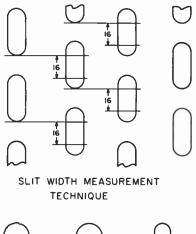

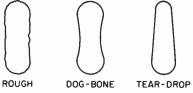

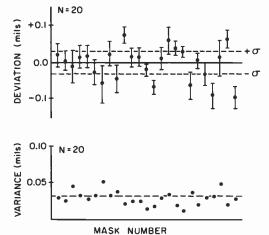

Figure 4 shows RCA's mask artwork system developed and assembled by a dedicated design automation (DA) group in Somerville, New Jersey. The heart of the system is a common artwork-specification design-file language (DFL). Designs can be created, modified and verified through a number of software programs. The initial design can be created by manual, interactive graphics, or by automated layout techniques as outlined on the top line of the schematic (Fig. 4). Similarly, modifications and verification of graphic designs can be accomplished by programs shown on either side of the diagram. For example, a design may be verified by CRITIC, the design-rule checking program. It is "batched" by the mask artwork program (MAP) for preparation of a magnetic tape that can drive various types of mask-generation equipment. One of these pieces of equipment is MEBES.