# RGA Engineer

Vol 18 No. 4 Dec|Jan 1972|73

### COS/MOS-a unique product line

In today's highly competitive semiconductor industry, it is a distinct advantage to have a popular product which the user instinctively associates with one particular supplier. There have been very few opportunities for this to happen in recent years because of the large number of producers throughout the world who aggressively seek to neutralize any momentary advantage of a competitor who introduces a new product to the market.

RCA has been able to build and sustain product association with COS/MOS (Complementary-Symmetry/Metal-Oxide-Semiconductor) integrated circuits. Beginning with the first commercial announcement in 1968, RCA has been associated with the development of this unique product line and with its ever-expanding capability. Initially there were many skeptics among both competitors and users who felt that the market for this technology would be limited to a few highly specialized applications which required extremely low power consumption. Consequently, it took considerable time and effort to expand the product line, educate customers, and thereby develop a general awareness that COS/MOS is a highly attractive, broadly usable product. Our success in the world marketplace is now very real and growing rapidly, as circuit and equipment designers have been convinced that they can make important advances in their products with COS/MOS. Other semiconductor makers, once skeptical, are now entering the market to participate in its exciting possibilities.

The papers in this issue illustrate the breadth of RCA effort. Contributions have been made by many individuals, only a few of whom are represented here. It is the high quality of this expanding activity which will retain our association with one of the most rapidly growing segments of the semiconductor industry.

Mattinger

William C. Hittinger **Executive Vice President** Consumer and Solid State Electronics Somerville, New Jersey

W. O. Hadlock

Editor

J. C. Phillips

Associate Editor

**RCA Engineer Staff**

J. P. Dunn

Art Editor

Mrs. Diane Ahearn Editorial Secretary

Mrs. Julianne Clifton Subscriptions

### **Consulting Editors**

C. A. Meyer

Technical Publications Adm., Electronic Components

C. W. Sall

Technical Publications Adm.,

Laboratories

F. J. Strobl

Technical Publications Adm.,

Corporate Engineering Services

### **Editorial Advisory Board**

R. M. Cohen

Mgr., Quality and Reliability Assurance, Solid State Div.

F. L. Flemming

VP, Engineering, NBC Television Network

C. C. Foster

Mor Technical Information Services, RCA Laboratories

M. G. Gander

Manager, Consumer Products Adm., RCA Service Co.

W. R. Isom

Chief Engineer, Record Division

L. R. Kirkwood

Chief Technical Advisor,

C. H. Lane

Div. VP, Technical Planning Electronic Components

Staff VP, Engineering

H. Rosenthal P. Schneider

Exec. VP, Leased Facilities

and Engineering Global Communications, Inc.

F. W. Widmann

Manager, Engineering Professional Development

Dr. H. J. Woll

Division VP.

Government Engineering

### Our Cover

. . features the rapidly expanding COS/MOS product line. "Pouring" forth are some of the many COS/MOS device packages; printed in the background are a few of the myriad applications. Cover photo: John Semonish, Commercial Engineering, Electronic Components, Clark, N.J.

Vol. 18, No. 4 Dec 1972 Jan 1973

A technical journal published by RCA Corporate Engineering Services 2-8, Camden, N.J.

RCA Engineer articles are indexed annually in the April-May Issue and in the "Index to RCA Technical Papers."

# R@// Engineer

• To disseminate to RCA engineers technical information of professional value • To publish in an appropriate manner important technical developments at RCA, and the role of the engineer • To serve as a medium of interchange of technical information between various groups at RCA • To create a community of engineering interest within the company by stressing the interrelated nature of all technical contributions • To help publicize engineering

achievements in a manner that will promote the interests and reputation of RCA in the engineering field • To provide a convenient means by which the RCA engineer may review his professional work before associates and engineering management • To announce outstanding and unusual achievements of RCA engineers in a manner most likely to enhance their prestige and professional status.

### **Contents**

| Editorial input              | ex-RCA'ers-pioneers in electronics                                                          | J. P. Dunn   F. J. Strobl                                          | 2  |

|------------------------------|---------------------------------------------------------------------------------------------|--------------------------------------------------------------------|----|

| Engineer and the Corporation | MOS—an RCA pioneered technology; COS/MOS—RCA's thrust in digital logic                      | H. Weisberg                                                        | 5  |

| COS/MOS                      | COS/MOS markets                                                                             | A. J. Bosso                                                        | 8  |

| design and development       | Fundamentals of COS/MOS integrated circuits                                                 | R. A. Bishop   D. R. Carley                                        | 10 |

|                              | COS/MOS standard-parts line comes of age                                                    | R. C. Heuner                                                       | 14 |

|                              | COS/MOS simplifies equipment design                                                         | R. E. Funk                                                         | 20 |

|                              | Development of COS/MOS technology                                                           | T. G. Athanas                                                      | 26 |

| applications                 | COS/MOS integrated circuits for consumer applications                                       | D. R. Carley                                                       | 31 |

|                              | Timekeeping revolution through COS/MOS technology                                           | S. S. Eaton                                                        | 35 |

|                              | Doing your own thing—COS/MOS custom design                                                  | G. J. Waas                                                         | 44 |

|                              | COS/MOS integrated circuits in the automobile environment                                   | D. K. Morgan                                                       | 47 |

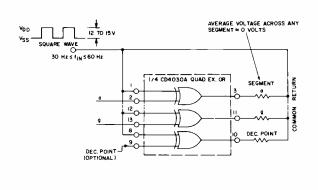

|                              | Liquid crystals and COS/MOS offer minimal-power digital displ                               | ays R. C. Heuner                                                   | 52 |

|                              | Keeping up with the times through computer-aided design                                     | J. Litus, Jr.                                                      | 56 |

|                              | COS/MOS is a high-reliability technology M.                                                 | N. Vincoff   Dr. G. L. Schnable                                    | 62 |

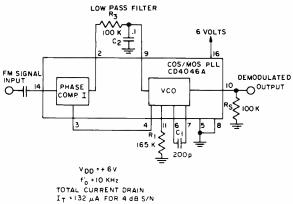

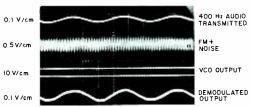

|                              | COS/MOS phase-locked-loop—a versatile building block for middigital and analog applications | cro-power<br>D. K. Morgan   G. Steudel                             | 69 |

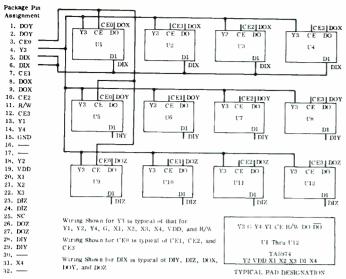

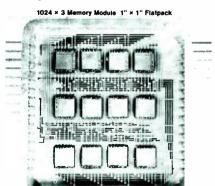

|                              | A multilayer, hybrid thin-film 1024x3 COS/MOS memory module                                 | Gargione   W. Keyzer   G. Noel                                     | 76 |

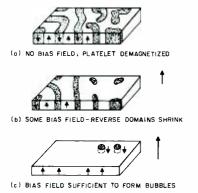

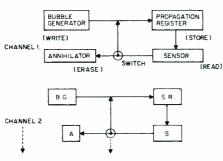

| Other                        | Magnetic bubble technology Dr.                                                              | A. Akselrad   L. S. Onyshkevych<br>r. R. Shahbender   C. Wentworth | 79 |

| Books                        | Books by RCA authors                                                                        |                                                                    | 86 |

| Notes                        | Transformerless full-wave rectifier                                                         | C. F. Wheatley, Jr.                                                | 88 |

|                              | Photomultiplier sensors with a continuously variable field of vi                            | ew P. de Bruyne                                                    | 88 |

| Departments                  | Pen and Podium                                                                              |                                                                    | 89 |

|                              | Dates and Deadlines                                                                         |                                                                    | 91 |

|                              | Patents Granted                                                                             |                                                                    | 93 |

|                              | News and Highlights                                                                         |                                                                    | 94 |

Copyright 1973 All rights reserved

# ex-RCA'ers pioneers in electronics

### J. P. Dunn | F. J. Strobl\*

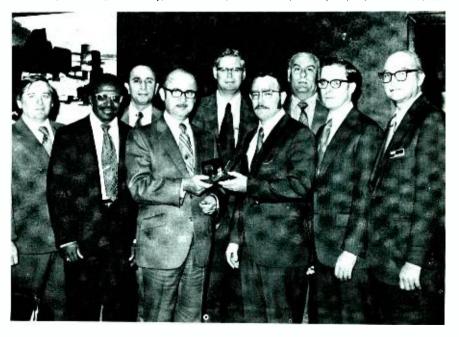

The editors had the privilege of taking a peek at a unique organization of former RCA radio and TV pioneers. This South Jersey group is unique in that it has no official name, rules, or regulations. Nor are there elected officers, dues, or formal agenda. But in spite of transgressing organizational theory, the group is functioning well.

This group, with the unofficial title of "the ex-RCA'ers," meets monthly. No serious business is conducted at these luncheon meetings. The members gather to renew old friendships and to swap tales of their activities during retirement. The most recurring topics heard at one meeting dealt with golf and travels.

Although loosely knit, the club has a common thread bonding the members. They have all had a stake in RCA's growth; and sometimes the talk turns to the business of the Corporation today.

The idea of a club composed of retired RCA people had its beginning in July, 1970. T. A. (Ted) Smith, after attending a retirement dinner for M. A. (Merrill) Trainer, wrote to Merrill: "Your luncheon yesterday was such a pleasant affair, with the opportunity to see people who had once been joined by the common bond of an early interest in television, that it seemed to me that there should be other times for getting together. I doubt that it would be possible to count on other retirements and so some other agency would be needed." Such an "agency" was soon to come into being.

\*Mrs. Dunn is Art Editor for the RCA Engineer; Mr. Strobl is Editor of TREND and Consulting Editor on the RCA Engineer.

Irving Wolff meet at the recent club meeting in Princeton.

Above (unofficial Vice President) Merrill Trainer during a pause that refreshes (ed. note thanks to Merrill for supplying much of the information contained in this editorial). At right, during dinner when conversation picks up.

Herman Gihring (center) and John Volkmann inspect the Holocard reader.

Stu Pike, Felix Cone and Ray Kell inspect mementos in the Sarnoff Library.

Sam Watson, Merrill Trainer, and Frank Strobl exchange ideas.

A group of electronic pioneers try out the Holographic identification System.

Steve Walton, Stan Cochran and Loren Jones exchange greetings.

David Sarnoff Library, alive with ex-RCA'ers.

R. Ballard and Ralph Holmes in "after dinner conversation."

Dinner served at the David Sarnoff Research Center.

Ted Smith at first envisioned "an informal, educational, non-profit organization to be known as the RCA System Video Pioneers, or RSVP." The purpose of RSVP would be "to hold a luncheon or a dinner once or twice a year in the South Jersey area at which time the advantages of the RCA Television System can be discussed, yarns can be swapped, and little known events of the early days of television can be revealed. Other projects might include preparing and distributing notes relating to the pioneering TV period."

After some discussion amongst Ted, Merrill, and Mul Brandt, they decided to start off with a luncheon at the Lorann House Restaurant in Westmont, N.J., on December 7, 1970. At this first meeting, there were 15 members present: T. A. Smith, M. A. Trainer, M. M. Brandt, K. B. Russell, J. E. Young, V. E. Trouant, L. E. Anderson, H. E. Gihring, S. W. Pike, C. D. Kentner, W. L. Lyndon, F. C. Blancha, J. E. Beezer, A. H. Turner, and N. M. Brooks.

As news of the club's formation spread (mostly by word-of-mouth) and the membership increased, the luncheons were moved to Compton's Log Cabin in Haddon Township. Again as the membership continued to grow, the meetings progressed in steps from the smallest private dining room at Compton's into their largest.

Generally, the club meets the second Monday of each month except for July and August. The May 1972 meeting was held at the David Sarnoff Research Center in Princeton, N.J. A sizeable group of the Princeton area residents shows up at all of the club's meetings. (One member even comes from Delaware.)

The membership roster has over 150 names, representing every RCA activity. At the September 1972 meeting, 90 members were present. Now,

### Roster of ex-RCA'ers

H. Albrecht H, E. Allen L. E. Anderson A. Rufus Applegarth R. C. Ballard Jay Barth Harry Becky A. V. Bedford G. L. Beers J. E. Beezer G. C. Bingham F. C. Blancha E. G. Bowman Harlan Breisford N. M. Brooks J. M. Brumbaugh W. W. Bullock Leonard B. Bureau E. C. Campbell C. O. Caulton S. W. Cochran F. E. Cone D. R. Creato E. L. Clark Thomas Consalvi A. N. Curtiss L. H. Davis E. T. Dickey E. A. Dodelin C. A. Dorner E. G. Dornfield Thomas T. Eaton A. E. Ertner D. J. Finn C. A. Fish N. Fisher L. E. Flory E. C. Foreman

L. T. Fowler F. A. Fuhrmeister H. E. Gihring G. S. Gilchrist M. S. Gokhale Paul E. Goley E. Dudley Goodale C. A. Gunther F. T. Hamilton Robert L. Harvey K. P. Havwood Roland S. Hemingway Roy A. Henderson J. Hertzberg **Harold Hoffer** Hollis Hoffman K. R. Hollister R. H. Holmes R. S. Holmes Walter Holt R. L. Holtzheimer A. R. Hopkins R. T. Huntington Aifred E. Jackson L. F. Jones W. L. Jones H. S. Kalvn A. S. Karker M. E. Karns H. M. Kearney R. D. Kell J. P. Kerrigan H. D. Knapp H. N. Kozanowski George Kraft G. A. Kumpf

Walter L. Lawrence

C. Leaig

F. S. Leroy

George Lindner J. E. Love W. L. Lyndon H. T. Macauley **Guy Manviller** A. F. Maugeri F. H. McCarthy W. P. Mercer, Jr. Benjamin Miller A. B. Mills F. W. Millspaugh C. C. More Harold D. Newton N. J. Oman S. W. Pike W. J. Poch J. E. Ploucher R. B. Prunty Charles Rammer S. Read, Jr. H. E. Reeber W. R. Reeves F. Rettenmever M. D. Riefler John H. Roe J. Roff C. A. Rosencrans E. W. Russell K. B. Russell J. W. Sanborn J. W. Sanderson J. N. Sanville Harvey Schock H. J. Schrader J. D. Seabert C. R. Sharpless Fred F. Shorvs C. M. Sinnett R. H. Slimm

J. P. Smith Paul V. Smith Ted A. Smith Charles S. Stickney B. D. Streeter A. C. Stocker A. H. Super E. F. Sutherland J. P. Taylor H. W. Taylor R. H. Teare W. M. Tomlin Merill A. Trainer V. E. Trouant R. J. Tullar A. H. Turner C. D. Tuska John Volkmann S. A. Walton **Albert Ward** S. H. Watson H. R. Wege R .R. Welsh F. W. Wentker R. P. Wetherald T. J. Whitney W. A. Willard G. H. Williams R. C. Willman George Wilson L. J. Wolf I. Wolff R. W. Wythes M. J. Yahr J. E. Young W. J. Zaun Carl W. Zemke V. K. Zworykin

the membership requirements have been relaxed to include anyone (ex-RCA) that had some early connection with RCA radio or television. Thus, engineers are in contact with their former associates in manufacturing, sales, marketing, and all other diverse activities that make a corporation function.

Since the members are old friends, no particular ceremony is followed at the meetings. Sometimes, there is a guest speaker. Often, a member will relate some interesting experience he has undergone. The informality of the club extends even to the method of paying for the luncheon tabs. A basket is passed around, and each member pays for what he eats plus gratuity and tax. This honor system not only works, but the basket usually contains enough left over to pay for postage and other items needed for meeting announcements.

Sociologists and psychologists today are emphasizing the problems that can arise with retirement. The transition from the working life is a shock to many retirees. But at the ex-RCA'ers meetings, the members seem more concerned with squeezing their many activities into each day. As one member said: "I think the reason we keep busy is that basically we have had interests all our lives. Our jobs kept us busy but we were always able to find other interests." This advice we should all consider carefully. The proof is there.

But the feeling that most pervades the club membership is that of pride—pride in knowing that their contributions have helped RCA become a giant in the electronics industry. After all, they have a grand total of over 4,500 years of experience.

### **Future Issues**

The next issue of the RCA ENGINEER, Vol. 18 No. 5, will contain representative papers devoted to radar and antenna engineering. Some of the topics to be covered are:

### Television receiving antennas

Communication antennas for Viking

G & CS antenna range

Advanced receiver techniques

Phase shifter design

Phased array design

Computer-aided antenna design

Discussions of the following themes are planned for future issues:

Transportation

Global communications

Broadband information systems

SelectaVision systems

Command and control

Broadcast and mobile communications

Engineering at RCA Ltd.

### **Engineer and the Corporation**

# MOS—an RCA pioneered technology; COS/MOS—RCA's thrust in digital logic

### H. Weisberg

Several of the advantages and applications of COS/MOS circuits are described in other papers in this issue. This paper reviews the development of COS/MOS logic circuits and projects some of the extensions of these circuits through 1975.

#### Harry Weisberg, Manager

COS/MOS IC and Liquid Crystal Operations Solid State Division Somerville, N.J

received the BSCE from City College of New York in 1944 and the MS in chemistry from Brooklyn Polytechnic Institute in 1960. He studied electronics at the University of Scranton. Upon graduation from C.C.N.Y., Mr. Weisberg joined E. 1. DuPont where his work involved the engineering aspects of industrial chemical products. He subsequently directed the developed of a line of new cellulose derivatives. Mr. Weisberg joined RCA in 1959, where he has worked in various design and process-development areas. He has contributed significantly to the design concepts incorporated into RCA's high-reliability and military-approved rectifier types. The RCA Thyristor and Power Rectifier Activity functioned under his design leadership from 1961 to 1965. During this time, he supervised and participated in the design of RCA's thyristor line. Mr. Weisberg was appointed Manager, Thyristor Product Development, in 1965. In early 1969, he assumed responsibility for COS/MOS design and technology. In 1971 he was appointed Manager of MOS IC and Liquid Crystal Products. In this capacity, Mr. Weisberg has responsibility for engineernig, manufacturing, and marketing. Mr. Weisberg holds three U.S. Patents and several foreign Patents involving new polymeric materials. He also holds five patents in semiconductor technology. Several additional patents are pending. He has contributed to Solid State Design and is a member of IEEE and American Chemical Society. Mr. Weisberg received the RCA Engineering Achievement Award in 1964.

Reprint RE-18-4-12 (ST-6110)

Final manuscript received September 25, 1972.

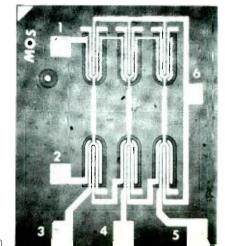

TEN YEARS AGO, at the IRE Electron Devices Meeting in Washington, D.C., Drs. Steven R. Hofstein and Frederick P. Heiman presented a paper describing the forerunner of today's vast variety of Mos logic circuits. Working under the direction of Thomas O. Stanley at the RCA Electronic Research Laboratory in Princeton, Drs. Hofstein and Heiman succeeded late in 1962 in developing a modest 50-by-50-mil array of 16 Mos transistors.

The complementary-symmetry concept for switching had intrigued RCA researchers as early as the 1950's, when T. O. Stanley experimented with unipolar complementary pairs. Significant contributions were also made by P. K. Weimer, et. al., in work with complementary TFT's. The advent of IC Mos technology paved the way for the practical application of complementary techniques to digital switching.

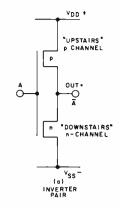

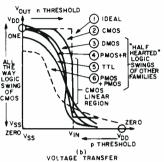

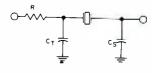

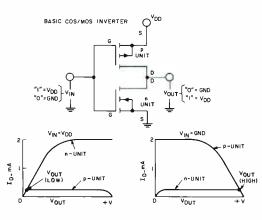

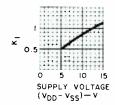

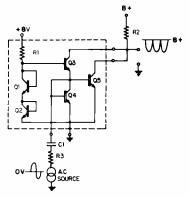

The basic building block for Mos is the inverter pair shown in Fig. 1a. Comparison of the switching characteristics and load lines for various combinations of complementary pairs shown in Fig. 1b and 1c clearly demonstrates why RCA's early research effort was directed toward the development of cos/Mos technology.<sup>2</sup>

### History and organization

G. B. Herzog and other researchers at the RCA Laboratories, recognizing the advantages that the p-channel/n-channel complementary pair would provide for switching as compared to the p-mos load-resistor combination, pushed hard toward the practical development of this technology. The task was later picked up in Lloyd Day's newly formed Microelectronics activity in Somer-

Fig. 1—COS/MOS inverter pair (a), and comparison of switching characteristics (b) and load lines (c) for various combinations of complementary pairs.

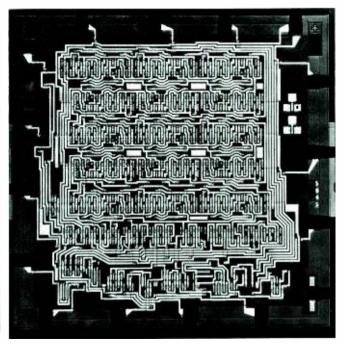

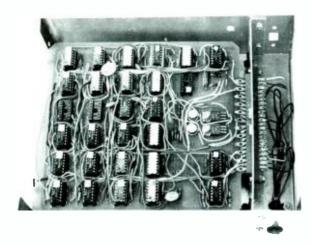

ville in the form of Princeton Applied Research projects. This effort resulted in the breadboarding of a cos/mos flipflop assembled from discrete inverters in June of 1963. With support from R. B. Janes' Advanced Development activity under the direction of P. D. Gardner, the team of R. D. Lohman and I. S. Kalish produced in 1964 what Fig. 2—Three-input COS/MOS NAND/NOR Gate developed in 1964.

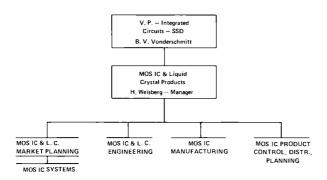

Fig. 3—Present organization of COS/MOS IC activity.

Fig. 4—Applications of COS/MOS integrated circuits.

#### **AUTOMOTIVE**

ELECTRONIC LOCKS

TACHOMETER/

SPEEDOMETER

FUEL-INJECTION

CONTROL

SPARK-ADVANCE

CONTROL

WIPER PAUSE CONTROL

CLOCKS

ADAPTIVE BRAKING

VEHICLE SAFETY CHECK

DRIVER CHECK

ELECTRONIC

TRANSMISSION

ANTI-WHEEL-SPIN AND

SPEED CONTROL

#### **DATA ACQUISITION**

INDUSTRIAL

MONITORING

SATELLITE READOUT

UTILITY-METER READING

AIRCRAFT FLIGHT-DATA

SYSTEM

PROCESS CONTROL

TRAFFIC CONTROL

ECOLOGY MONITORING

D/A AND A/D

CONVERTERS

#### **COMPUTERS**

PARALLEL/SERIAL

COMMUNICATIONS

BUFFERS

COMPLETE AEROSPACE

COMPUTERS

REMOTE TERMINALS

PERIPHERAL BUFFERS

POCKET CALCULATORS

SERIAL CONTROL

COMPUTERS

SCRATCH PAD

MEMORIES

MAIN MEMORIES

### COMMUNICATIONS

POCKET PAGERS

SELECTIVE CALL

FREQUENCY

SYNTHESIZERS

DIGITAL FILTERS

PULSE-PAIR DECODERS

PRESET CHANNEL

MEMORY

PHASE-LOCKED

OSCILLATORS

REMOTE TUNING

CATV CONVERTERS

### TELEPHONE

TONE SYNTHESIZING

TONE DETECTION

SOLID-STATE

CROSSPOINTS

DIAL-PULSE

CONVERTERS

REPERTORY DIALER

DIGITAL PBX

DELTA-MOD

CONVERTERS

AUTOMATIC REDIAL

### **MEDICAL**

BLADDER CONTROL LUNG STIMULATION HEART PACERS PROSTHETIC CONTROL PORTABLE INSTRUMENTATION AUTOMATIC PATIENT MONITORING

### APPLIANCES

SPEED/TIME CONTROL

HEAT/TIME CONTROL

'NDUSTRIAL

SEQUENCERS

'WASHER AND DRYER

TIMERS

AUTOMATIC COOKING

CONTROLS

DIGITAL CLOCKS

TOUCH CONTROLS

### **ADDRESSING**

DEMOLITION-FUZE DETONATION INTERROGATION OF SATELLITES RESOURCE MONITORING BY SATELLITES

### **CLOCKS AND TIMERS**

WRIST WATCHES

AUTO CLOCKS

JIGITAL CLOCKS

BATTERY WALL CLOCKS

VAVIGATION CLOCKS

ENVIRONMENTAL

SAMPLING TIMERS

INDUSTRIAL TIMERS

DOWN-TIME CLOCKS

### **FUZES**

FREE-FALL COUNTER VAR-TIME FUZE SELF-DESTRUCT FUZE ELECTRONIC LOCKS FOR WARHEADS DEMOLITION RECODER was probably the first cos/mos IC, a three-input NAND/NOR gate (Fig. 2).

The significance of this technological achievement was not lost on Art Liebschutz, who was then reporting to Ben Jacoby in his capacity as digital marketing manager. The Microelectronics group in 1965 was hard at work on the development of a low-power DTL circuit for the digital market.

In 1966, the forerunner of the present cos/mos activity combined both bipolar and mos digital functions under J. Ritcey (followed by E. E. Moore in 1968) as engineering manager, F. J. Rohr and A. J. Bosso in marketing, and B. V. Vonderschmitt in design and applications for both digital and linear. The present organization, shown in Fig. 3, follows the product-line concept introduced by W. C. Hittinger with the formation of the Solid State Division in 1970. The liquid-crystal activity has been incorporated into the cos/mos product line in recognition of the strong interaction and interdependence of the two technologies.

### **Advantages of COS/MOS**

The micropower dissipation, high noise immunity, wide operating-voltage range (3 to 15 V), and temperature range (-55°C to +125°C for ceramic and -40°C to 85°C for plastic) are well known advantages of cos/Mos. Also important is the ease of converting and implementing logic functions in integrated-circuit form to system applications.

These attributes have resulted in a versatility of applications, some of which are better or more economical because of cos/mos and some of which wouldn't be possible with any other technology. Some of these applications are illustrated in Fig. 4.

### Standard vs. custom

RCA's announcement of the availability of commercial cos/Mos circuits in 1968 resulted in about 15 standard circuits by 1969. This small selection, compared with more than 200 bipolar standard logic circuits, and the lack of second sourcing for cos/Mos resulted in difficulties in getting product acceptance. Today, RCA's CD4000 series consists of over 60 standard circuits,

virtually all of which are second sourced by major solid-state integratedcircuit manufacturers.

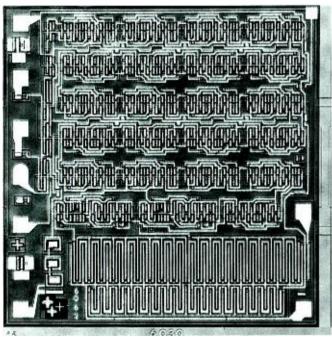

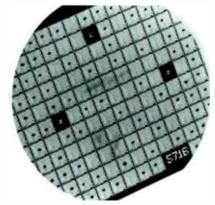

From the beginning, the feasibility of MSI and LSI using cos/Mos technology was an attractive feature. Early support by NASA resulted in the development of custom LSI circuits. The CD4057A began as a NASA-funded custom circuit development, the TA5716. It is primarily a four-bit central processor which contains a shift/ store register in addition to the arithmetic and control circuits. Sixteen separate processing and logic operations can be performed, including the logical AND, EXCLUSIVE OR, and OR. The processing operations include COUNT UP, COUNT DOWN, SUBTRACT, ADD, and SHIFT (left and right). Applications include portable-battery-operated compact computers, or equipment in which noisy environments are encountered.

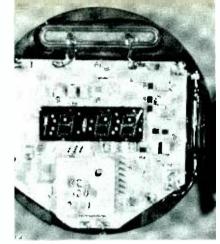

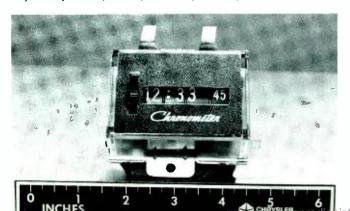

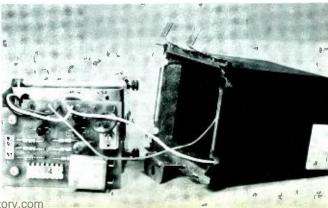

More than 50 custom circuits have been developed since the TA5716, and about as many are presently in various stages of development. Custom cos/ mos circuits are being sold for various watch and clock applications, heart pacers, satellites, pocket pagers, fuzes, and many other functions.

To participate in this vast and varied systems world, RCA must interface with customers at many levels. Accommodating the many and varied needs of customers is perhaps the greatest challenge to continued success. It is no longer possible to sell devices and simply provide applica-

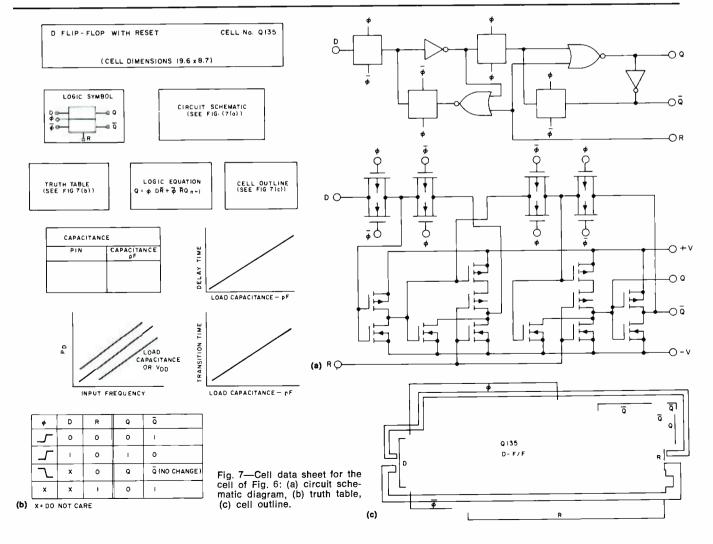

Fig. 5-Typical example of standard cell.

-Beam-lead version of CD4013A

tions assistance in the traditional manner; ic manufacturers must be prepared to do that and much more. Participation in the wide spectrum of supplying system support can range from processing wafers with fully designed masks to designing a system on a chip with only function parameters provided and specifying outboarded components as well. RCA, like other manufacturers, is being challenged to develop a far greater breadth of skills than has traditionally been the component-suppliers' contribution.

RCA's design automation facility and capabilities have been described elsewhere.3 This activity has progressed from a drafting and digitized maskgeneration facility to a sophisticated CAD facility with an extensive library of standard cells, such as that shown in Fig. 5. The combination of standard cell and metal routing routines allows the designer the full gamut of compromise between time optimization and maximum efficiency of packing density. RCA will continue to develop and expand the repertoire of standard circuits to meet customers' demands and serve their specific custom needs.

### Extension of COS/MOS technology

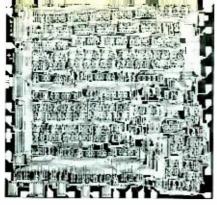

Using the complementary mos inverter shown in Fig. 1a as the basic functional-cell building block, new technology will develop to enhance cos/ mos as a desirable and economical digital integrated-circuit form. Currently under development is the modification and adaptation of beam-lead techniques to Mos. The Solid State Technology Center has already produced experimental beam-lead designs for the CD4000A, the CD4007A, the CD4013A (shown in Fig. 6), and sev-

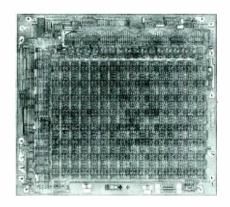

COS/MOS timing circuit

eral others. The first beam-lead circuits for commercial applications were delivered this year, and the technology will be extended into the standard product line in 1973.

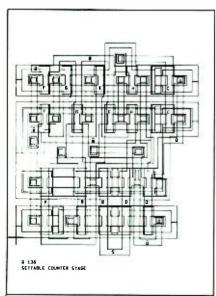

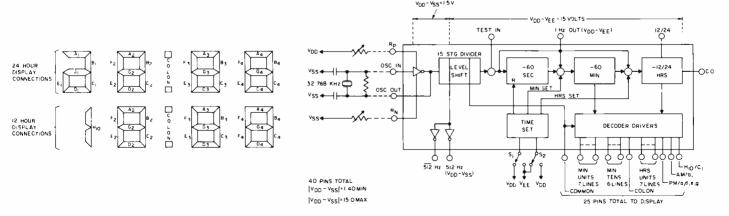

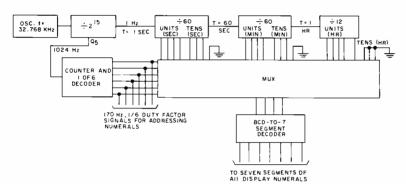

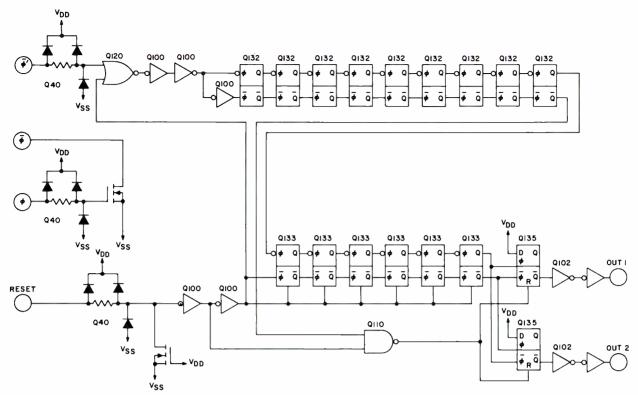

The main thrust of new technology will be to increase function density, speed/power capability, voltage range, and LSI capability, as shown in Table I. This improvement will have to be accomplished at planned cost reductions. To aid in packing-density improvement, multilayer metallization utilizing polycrystalline silicon, jon implantation, and self-aligning silicon gate techniques are being evaluated. Fig. 7 shows the layout of a timing circuit comprising an oscillator inverter, a counter divider from 32-kHz to 1-Hz output, a divide-by-60 stage for minutes, a divide-by-12 stage for hours, and a BCD-to-seven-segment output stage for digital display of hours, minutes, and seconds.

Polycrystalline silicon gate circuits have been produced for use in watch circuits that will operate from a singlecell mercury battery to an end-of-life rating of 1.1 V. It is theoretically possible to design cos/mos to operate from power sources as low as 0.5 V. Cos/mos on sapphire, commonly known as sos, will allow higher speed power values of 1 pJ to be reached with propagation delays of 5 ns.

Cos/mos has undoubtedly achieved a place in the designer's collection of circuit logic forms for systems development.

### References

- Integrated Circuits Course. "The Electronic Engineer," (Chilton. Philadelphia, Pa.).

Cushman, R. H. "CMOS Finally Gets it all Together" EDN (June 1952).

- 3. Design and Automation Test Technology Section, RCA Engineer, Vol. 17, No. 3 (Oct.-Nov. 1971)

Table I—COS/MOS present capabilities and future plans.

|                                                                                                     | 1968    | 1972        | 1975      |

|-----------------------------------------------------------------------------------------------------|---------|-------------|-----------|

| Gate complexity Maximum chip size (mils) Maximum clock frequency (MHz) Voltage-range capability (V) | 40      | 500         | 3000      |

|                                                                                                     | 80 x 80 | 150 x 190   | 300 x 300 |

|                                                                                                     | 5       | 15          | 50        |

|                                                                                                     | 6 to 15 | 1.0 to 20.0 | 0.5 to 25 |

# COS/MOS markets

### A. J. Bosso

The market for COS/MOS integrated circuits is as broad as the spectrum of logic applications. The advantages of complementary-symmetry logic have long been known and desired; it remained for the Solid State Division, with its COS/MOS line of circuits, to make these advantages economically feasible and, therefore, available to the full range of electronic-equipment manufacturers.

THE PRIMARY ADVANTAGES of complementary-symmetry circuits, and of cos/mos in particular, are:

### Circuit advantage

Wide operating-voltage range (3V to 15V)

Extremely low power dissipation (typically 10nW/gate)

High noise immunity (typically 4.5V at a  $V_{\rm DD}$  of 10V, theoretically  $V_{\rm DD}/2$ )

Tolerance of cos/mos to its total environment (tolerance to supply voltage, noise, temperature, transistor parameters)

Only one power-supply voltage and one clock phase is required

With advantages such as those listed above and with the economy provided by high yields, MSI/LSI functions (both standard and custom), and plastic packaging, it is easy to understand why cos/Mos is extending the spectrum of electronic logic to applications which were not electronic previously. One of the primary examples is the watch and clock market. It is now possible to wear a wristwatch that is accurate to a minute a year and that runs continuously for a year on a single 1½-volt

Reprint RE-18-4-6

Final manuscript received October 11, 1972.

### User benefit

Less regulation of power supply required.

Immunity to power-supply or ground-line noise.

Makes possible operation of large logic systems from battery power supply.

Substantially reduces conventional power-supply size and regulation requirements and, therefore, total power-supply costs.

Lower power dissipation reduces substantially or eliminates auxilliary cooling systems and, therefore, the associated weight, space, and costs

Lower power dissipation permits closer packing of circuits and, therefore, increases packing density of equipment.

The cos/mos circuits are ideal for applications in which external electrical noise ambients are encountered.

Relatively low speed of cos/mos circuits does not generate noise.

Noise immunity of cos/mos circuits is virtually constant over the full temperature range.

Facilitates system design and saves engineering time. Lack of criticality and "fine tuning" requirements means cos/mos "works the first time."

Absence of criticality means smoother-running production lines.

COS/MOS tolerance to its total environment means better operating reliability.

Easier and more reliable system design.

Andrew J. Bosso, Mgr.

MOS-IC Market Planning

Solid State Division

Somerville, New Jersey

received the BSEE from Penn State in 1957 and joined RCA's Solid State Division in the same year. He worked as an applications engineer for digital-switching transistors until 1960 when he was made Engineering Leader of digital-switching transistor applications. In 1967, Mr. Bosso was made Market Planner for COS/MOS IC's, and in 1971 was made Manager, MOS-IC Market Planning.

cell for a price far lower than that of a conventional mechanical chronometer.

### Clock and watch market

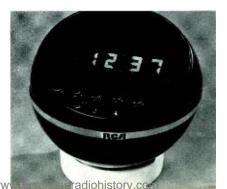

Truly, the cos/mos watch is a secondary time standard on your wrist. Before the advent of cos/mos, this kind of performance was limited to laboratory instruments at prices of hundreds to thousands of dollars. By 1975, a significant number of watches will be built using quartz crystals and cos/mos, and the retail price will be under \$50. By 1980, 50 to 75% of watch production will be electronic

with retail prices comparable to any in the industry. In addition to watches having motor-driven conventional hands, digital watches using a single cos/mos LSI chip and either liquid crystal or LED displays will be available shortly.

### **Automotive market**

Federal pressure for control of emissions and for increased safety provisions on automobiles, some of it in the form of legislation, is increasing. To meet the federal requirements, more logic circuits will be used in automobiles. With its wide operating voltage range (almost exactly matching the excursions of the automobile "12-volt" supply) and high noise immunity, cos/mos is a natural for automotive applications, and is being used extensively for programs which will mature in the near future as well as for advanced-systems work.

### Aerospace and military markets

But it is not only in new markets that the advantages of cos/mos are attrac tive. Certainly cos/mos has proven very attractive in aerospace applications. The very low power dissipation, together with the packing density which it permits, have provided a much needed means of accomplishing a greater number of tasks per satellite within given power and weight constraints than was possible previously. For space applications and for critical military and industrial applications, the Solid State Division is currently in the process of qualifying the cos/mos line to MIL-M-38510. The qualification process should be complete in the fourth quarter of 1972, and qualified

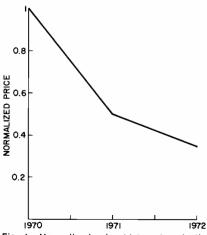

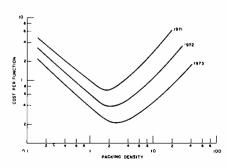

Fig. 1—Normalized price history for plastic-packaged COS/MOS circuits.

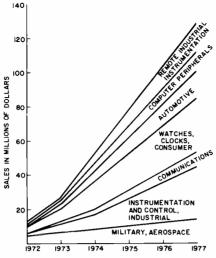

Fig. 2—Projected COS/MOS sales by market category.

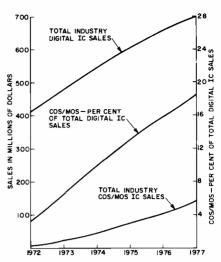

Fig. 3—Comparison of total COS/MOS sales with total industry sales for all digital IC's.

parts to MIL-M-38510 specifications should be available beginning in the first quarter of 1973.

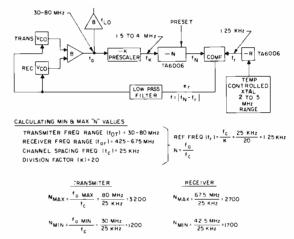

In military applications, cos/mos is being used very extensively in munitions-fuze applications, in avionics (navigation, fire control, communications equipment, etc.), in ground communications (frequency synthesizers for both portable and base-station equipment), and for intrusion systems.

### Industrial and consumer markets

In the industrial and consumer markets, cos/mos is proving itself cost effective, as well as operationally attractive, when compared to such technologies at TTL and HTL. RCA's introduction, in 1970, of economical plastic-packaged cos/mos Ic's was a major breakthrough in cos/mos ic production costs. Fig. 1 shows the normalized price history for plastic-packaged cos/mos circuits. Customers are now beginning to report back that, in many systems, the savings in powersupply costs, as well as the space and weight savings resulting from the elimination of blower fans and heat sinking, have given them a total cost savings and made their equipment more competitive. In many instances, the wide choice of cos/mos circuits and/or custom circuits also has helped to reduce package count. But the best feedback is perhaps the simplest, that is the comment, "This stuff is great to work with. My system worked the first time." What better way to describe the

advantage of the great tolerance of cos/mos to its total environment?

In 1972, 70% of the cos/mos circuits sold will go into non-military applications. This percentage will increase rapidly in the next few years. Some typical non-military applications are personal remote pagers, modems, process control and other specialized computers, data-buoy instrumentation, test and measurement instruments, telephone control logic, remote utilitymeter-reading equipment, industrial controls, commercial avionics, and commercial communications equipment. In the not too distant future, the price of cos/mos circuits will permit their use in home-entertainment applications, such as frequency synthesizers for FM radios and TV sync circuits. Fig. 2 shows projected cos/mos-IC sales by market category for the years 1972 through 1977.

### Conclusion

The exact manner of implementing the circuits will change, and increases in speed performance will occur, but the basic operating advantages and cost effectiveness of cos/Mos circuits will continue to earn their place in the logic-circuit market. Fig. 3 shows total industry sales for all digital Ic's and cos/Mos together with cos/Mos sales as a percentage of the total. Both the cos/Mos technology and the RCA Solid State Division will be major factors in the total logic circuit market by 1975.

# Fundamentals of COS/MOS integrated circuits

R. A. Bishop | D. R. Carley

The development of the technology that makes possible simultaneous fabrication of n-channel and p-channel metal-oxide-semiconductors (MOS) transistors on the same semiconductor pellet has given rise to a new family of monolithic integrated circuits, i.e., the RCA series of complementary-symmetry/metal oxide semiconductor (COS/MOS) devices. This paper discusses the MOS transistors used in COS/MOS integrated circuits, describes basic COS/MOS building-block elements, and explains the built-in protection against high-voltage transient and inherent high noise immunity of RCA COS/MOS integrated circuits. In addition, the major performance characteristics of COS/MOS devices are compared with those of other commercially available digital integrated circuits.

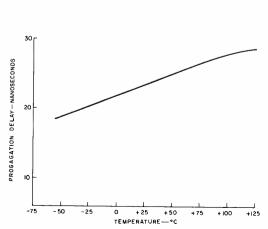

THE BROAD LINE OF RCA COS/MOS integrated circuits includes more than 50 standard types. In addition, almost one hundred custom types are in various stages of design, development or production. These devices feature extremely low quiescent dissipation with wide voltage tolerance, excellent noise immunity, single-phase clocking capability, and moderate speed performance. Moreover, RCA cos/mos integrated circuits are capable of operation over a supply-voltage range of 3 to 15 V and over an operating-temperature range of -55°C to +125°C for types supplied in ceramic packages or -40°C to +85°C for plastic-package types.

Reprint RE-18-4-21 (ST-6085)

Final manuscript received September 25, 1972.

### **COS/MOS** transistors

In metal-oxide-semiconductor (Mos) transistors, the metal gate electrode that controls the conduction between the two ohmic contacts (called source and drain) is separated from the semiconductor conduction channel by an oxide insulation layer. The two basic types of mos transistors are enhancement types and depletion types. All mos transistors used in cos/mos integrated circuits are enhancement types. The enhancement type of mos transistor remains in the off state for an input gate bias of 0 V with respect to the source. Conduction must be "enhanced" by the application of a bias voltage to the gate electrode in the proper polarity to turn on the transistor.

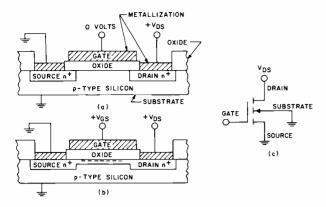

Fig. 1 shows cross-sectional diagrams of an n-channel enhancement type of mos transistor for both off-state and on-state conditions. The source and drain regions are formed by n-type diffusions in a p-type substrate. In the off state (i.e., when the gate-to-source voltage  $V_{as}$  is 0 V, shown in Fig. 1), a high degree of isolation exists between the source and the drain (typically 10,000 megohms for a drain-tosource voltage  $V_{ns}$  of 10 V). As the gate is made positive with respect to the source and the substrate, electrons are attracted to the p-type area between the source and the drain beneath the insulating oxide.

If the gate is made sufficiently positive with respect to the source, *i.e.*, becomes greater than the threshold voltage  $V_{TH}$  the number of electrons attracted to the semiconductor region between the source and the drain is large enough to change the surface conduction of this region from p-type to n-type, and an n-type conduction channel is provided from source to drain, as indicated in Fig. 1b.

Fig. 1c shows the schematic symbol for an n-channel enhancement type of mos transistor. The enhancement-mode feature is indicated in the symbol by the dashed line (channel) that connects the source and drain electrodes. The interruptions of this line are used to show that the channel is "open" unless conduction is enhanced by application of a forward gate bias.

The operation of a p-channel enhance-

**Ed. Note:** Mr. Carley's biography and photograph are included in his other article in this issue.

### R. Adrian Bishop

COS/MOS Applications RCA Solid State—Europe Sunbury-on-Thames, England

received the Higher National Certificate in Applied Physics in 1964 from Slough College of Technology. In 1965 he gained endorsements in Electronic Engineering. While studying, Mr. Bishop worked on the development of semiconductor materials at Frigister Laboratories. He next joined Electro-mechanisms as a design engineer working on circuitry for transducer measuring systems. In 1967, he moved to International Computers, Ltd., as a project leader in the circuit and memory technology department. He joined RCA at Sunbury, England in 1970 as an applications engineer in the COS/MOS group. Mr. Bishop is a Graduate of the Institute of Electronics and Radio Engineers and as Associate of the Institute of Physics.

Fig. 1—N-channel MOS transistor: (a) OFF-state condition; (b) ON-state condition; (c) schematic symbol.

Fig. 2—P-channel MOS transistor: (a) OFF-state condition; (b) ON-state condition; (c) schematic symbol.

ment type of mos transistor is the same as that of the n-channel type except that n- and p-type regions, voltage polarities, and directions of current are reversed. In p-channel Mos transistors, positive charges (holes) are the current carriers in the channel, rather than electrons as in n-channel devices. Figs. 2a and 2b show the onand off-state conditions for a p-channel enhancement type of Mos transistor, and Fig. 2c shows the schematic symbol for this type of transistor. As the gate-to-source voltage  $V_{gs}$  is made more negative, a low-resistance (ptype) conduction channel develops between the p-type source and drain regions.

The polarity type of the Mos transistor is indicated in the schematic symbol by the orientation of the arrow at the junction between the channel and substrate. The arrow points to the more negative terminal (channel in n-channel devices or substrate in p-channel devices) of the substrate-to-channel junction.

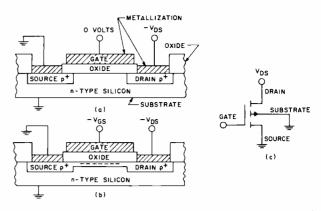

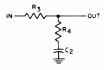

## Basic COS/MOS circuit elements Inverter

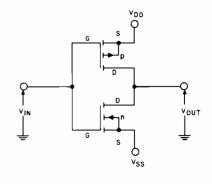

One of the most basic circuit elements used in cos/mos integrated circuits is the inverter. The cos/mos inverter consists simply of a complementary pair of n- and p-channel transistors connected in series. In addition to the inverter, there are three other basic circuits that are used extensively in cos/mos devices. These include the transmission gate, the NOR gate, and the NAND gate. Almost all cos/mos integrated circuits, regardless of complexity, are implemented by use of one or more of these four basic elements.

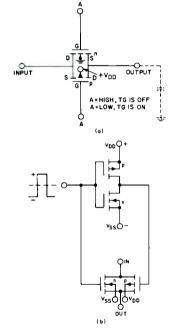

Fig. 3 shows the circuit diagram for the basic cos/mos inverter. The notations S, D, and G indicate the source, drain, and gate connections, respectively, for each transistor. The p and n notations indicate p-channel and n-channel devices. The voltage  $V_{nb}$  is the most positive voltage in the circuit, and the voltage  $V_{\kappa\kappa}$  is the lowest or most negative voltage, usually ground.

When the input to the inverter is at zero volts (logic 0), the p-channel transistor is turned on, and the n-channel is turned off. Under these conditions, a low-impedance path exists from the output to  $+V_{pp}$ , and a very high impedance exists between the output and ground  $(V_{ss})$ . The output voltage, therefore, approaches  $+V_{DD}$ (logic 1) under normal loading conditions. When the input is at  $+V_{DD}$ (logic 1), the situation is reversed. and the output approaches zero (logic 0). In either state, under normal loading, the output levels are within 10 mV of the  $+V_{DD}$  or ground  $(V_{SS})$ voltages; the logic swing, therefore, is virtually equal to the power-supply

In either logic state, one Mos transistor is on while the other is off. As a result, the quiescent power consumption, which is equal to the product of the supply voltage and the off-unit leakage current, is extremely low. With a supply voltage of 10 V and a typical off-unit leakage of 0.5 nA, the quiescent power dissipation is only about 5 nW in either logic state.

During switching transitions, the power dissipated in the cos/Mos inverter increases. Both the p-channel

and the n-channel transistors are partially on during the transition time; therefore, some current can flow through the channels from the supply voltage  $(V_{nn})$  to ground. Also, any output load capacitance must be charged through the p-channel transistor as the output switches to the high level. Similarly, the stored energy must discharge through the n-channel transistor during the transition to a low output. The power dissipated during switching is usually the power required to charge the capacitance of the subsequent stage and is equal to  $C_{n}V_{nn}^{2}f$ , where  $C_{n}$  is the output capacitance,  $V_{pp}$  is the supply voltage, and fis the operating frequency in Hertz.

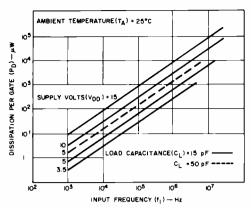

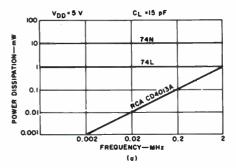

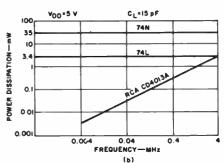

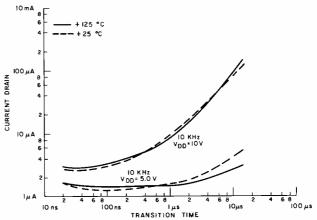

The dynamic power consumption increases linearly with increasing frequency and node capacitance. Fig. 4 shows a typical curve of dynamic power dissipation as a function of frequency. At 1 MHz, the dissipation for a simple cos/mos gate is in the order of 1 mW.

| VIN | р   | n   | Vout |

|-----|-----|-----|------|

| VSS | ON  | OFF | V DD |

| VDD | ÒFF | ON  | Vss  |

Fig. 3—COS/MOS inverter

Fig. 4—Typical dissipation characteristics of a COS/MOS gate circuit as a function of frequency.

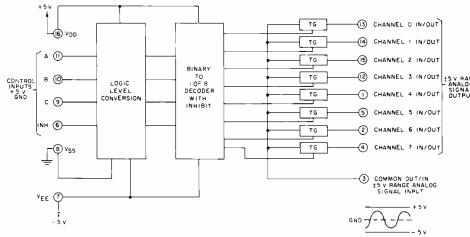

Fig. 5—Transmission-gate circuits: (a) basic COS/MOS transmission gate; (b) combination of transmission gate and inverter to form a basic switching circuit.

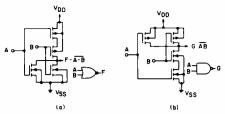

Fig. 6—COS/MOS logic gates: (a) two-input NOR gate; (b) two-input NAND gate.

#### Transmission gate

The transmission gate, basically, is a single-pole single-throw switch that has a very high off-to-on resistance ratio (typically, in the order of 10°). This circuit is formed by connecting two complementary mos transistors in parallel, as shown in Fig. 5a. When the control signals are applied as indicated, the circuit functions as a bidirectional switch and provides either low on or high off impedance to input signals between ground and  $+V_{nn}$ . The transmission gate, together with an inverter which provides the appropriate control inputs, is used extensively as a coupling element in latches, flip-flops, shift registers, and counters and to provide a three-state output circuit. It is also used as an analogue switch with high linearity in audio and video switching applications. Fig. 5b shows the combination of a transmission gate and an inverter to form a basic switching circuit.

### NOR and NAND logic gates

A NOR gate is formed by connection of two or more paralleled n-channel transistors in series with two or more series-connected p-channel transistors. Fig. 6a shows the circuit diagram for a two-input NOR gate. A negative output is obtained from this gate circuit when either input A or input B is positive. For each condition, the n-channel transistors are turned on and the p-channel transistors are turned off so that the output is connected to  $V_{ss}$  (or ground).

A NAND gate consists of two or more series-connected n-channel transistors in series with two or more parallel-connected p-channel transistors. Fig. 6b shows the circuit diagram for a two-input NAND gate. The output of this circuit is low  $(V_{ss})$  only if both inputs are high  $(V_{nn})$ , because only in this way are both n-channel transistors turned on to connect the output to  $V_{ss}$ .

Multiple-input NOR and NAND gates are implemented by adding more transistors. For instance, a four-input gate would have four n-channel transistors and four p-channel transistors. More complicated devices are composed of many devices. A basic D flip-flop has eight p-channel transistors and eight n-channel transistors, a JK flip-flop has fifteen n-channel transistors and fifteen p-channel transistors, and a static RAM memory cell has two n-channel transistors and two p-channel transistors plus two additional p-channel types for cell selection. In general, the cos/mos chip area needed for these complicated circuits is considerably less than the area required by the popular TTL technology. For example a cos/mos D flip-flop cell is 21/2 times smaller than the TTL version. Complex cos/mos circuits with many hundreds of gates on a single chip are being manufactured.

### Input protection

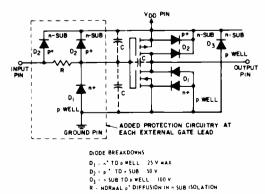

The input impedance of cos/mos integrated circuits is extremely high because of the insulating oxide layer at the gate input. Like all mos circuits, if a cos/mos device is out of circuit or if an input is unconnected, a static charge can be built up on the input parasitic capacitance. If the input is allowed to exceed 100 V, the gate oxide layer will be damaged. RCA. cos/mos integrated circuits have a built-in diode protection network at all inputs. This input protection network clamps transient voltages to safe levels. Fig. 7 shows the network used in RCA CD-4000A series devices. The

Fig. 7—Input protection circuit used with RCA COS/  $\ensuremath{\mathsf{MOS}}$  integrated circuits.

Table I-Logic characteristics.

| Logic<br>type | I)C<br>power<br>dissipation<br>(mW/Gate) | Prop<br>delay<br>(nS) | DC noise<br>immunity<br>(V) | DC<br>fan out | Logic<br>swing<br>(V) |

|---------------|------------------------------------------|-----------------------|-----------------------------|---------------|-----------------------|

| RTL           | 19/5                                     | 12                    | 0.1                         | 5             | 1                     |

| DTL           | 11                                       | 30                    | 1                           | 8             | 2.8                   |

| TTL           |                                          |                       |                             |               |                       |

| 74            | 10                                       | 13                    | 1                           | 10            | 3.3                   |

| 74L           | i                                        | 35                    | 1                           | 10            | 3.3                   |

| HTL           | 44/13                                    | 110                   | 6.5                         | 10            | 12.5                  |

| ECL           | 25                                       | 2                     | 0.27                        | 25            | 0.9                   |

| COS/MOS       | 0.00001                                  | 25                    | 45% of Vnn                  | > 500         | up to 15 V            |

distributed input resistor provides current limiting and together with the parasitic capacitance of the protection diodes forms an integrating network which slows down very fast transients so that sufficient time is allowed for the protection diodes to perform their voltage clamping function. Normal switching operation of the cos/Mos device is unaffected by this network.

### **Noise immunity**

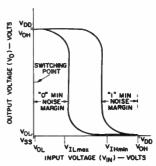

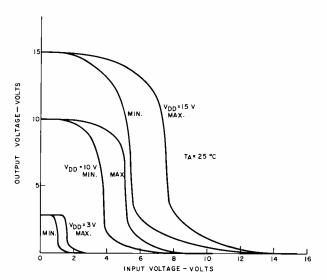

The complementary structure of the inverter results in a near ideal inputto-output transfer characteristic. The switching point is typically midway (45 to 55%) between the 0 and 1 logic levels. As a result, the inverter has high DC noise immunity because the output does not switch until the input voltage rises to nearly half the supply voltage  $V_{nn}$ . This behavior is shown in Fig. 8 for  $V_{nn}$  voltages of 5, 10, and 15 V. This figure also shows the insensitivity of the transfer characteristic to changes in ambient temperatures over the range from -55°C to +125°C.

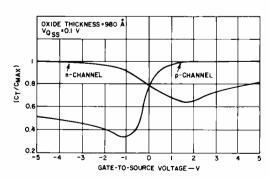

The switching-point voltage depends on the match in the impedances of the n-channel and p-channel transistors rather than on absolute transistor threshold voltages. Transistor characteristics are matched by the design of appropriate size devices and by controlling transistor threshold voltages. Normally, the channel width of pchannel transistors is twice that of corresponding n-channel transistors because of the lower charge-carrier mobility of p-channel types. Fig. 8 shows that, in the typical case, the switching point is maintained at 45% of the supply voltage  $V_{DD}$  over the supply range of 3 to 15 V because of this dependence on the matching of the two transistors rather than an absolute transistor threshold.

In production of cos/Mos integrated circuits, a range of maximum and minimum transfer characteristics re-

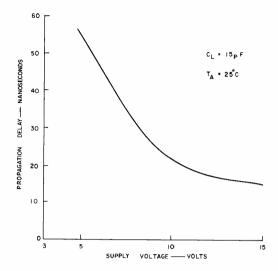

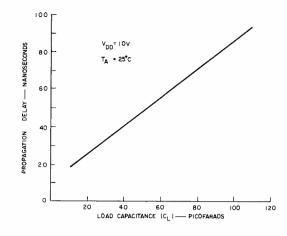

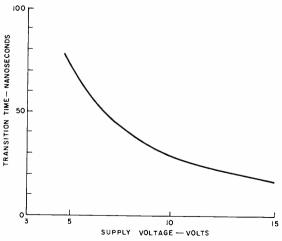

sults among different devices of the same type because of normal manufacturing-process tolerances, as shown in Fig. 9. The actual spread in switching point provides a guaranteed DC noise-immunity value equal to 30% of the supply voltage. Noise immunity increases as the input noise pulse width becomes less than the propagation delay of the circuit. This condition is often described as AC noise immunity. Standard cos/mos circuits have moderate switching speed (in the order of 35 ns at a  $V_{nn}$  of 5 V) and good DC noise immunity; AC noise immunity, therefore, is excellent.

### COS/MOS vs. other logic types

The basic characteristics of cos/Mos integrated circuits compare very favorably with those of other integratedcircuit logic families. Table I compares the static power dissipation, noise immunity, and other characteristics of cos/mos devices with those of other familiar types of digital integrated circuits. A prime advantage of cos/mos devices, as compared to TTL devices, for example, is low power dissipation. Because the power consumption of cos/mos devices decreases linearly with frequency, as shown in Fig. 10, these devices offer a considerable power saving for many logic systems in which a large proportion of the logic operates at relatively low frequency.

The wide supply range of 3 to 15 V can allow operation from simple, wide-tolerance, low-current power supplies or inexpensive batteries. In addition, the moderate switching speed avoids many of the noise and transmission line reflection problems associated with faster forms of logic. The high noise immunity is a desirable feature in many applications. In general, these characteristics simplify the design of logic systems and can provide performance improvements in many general- and special-purpose applications.

Fig. 8—Typical voltage transfer characteristics for a COS/MOS inverter.

Fig. 9—Minimum and maximum transfer characteristics for a COS/MOS inverter.

Fig. 10—Speed-power product of COS/MOS and TTL devices: (a) quad gate; (b) flip-flop.

# COS/MOS standard-parts line comes of age

### R. Heuner

A major advantage of COS/MOS is the ability of the circuit to perform well in single gates and flip-flops as well as in complex MSI and LSI configurations. Much information is available on the unique characteristics and advantages of the COS/MOS circuit configuration. This paper illustrates the broad foundation of COS/MOS standard parts and explains why COS/MOS is the correct circuit configuration for such a broad-based line of parts.

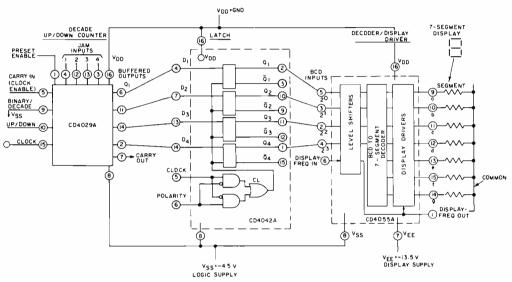

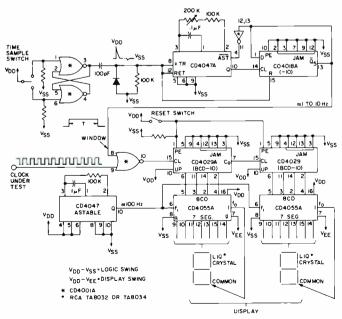

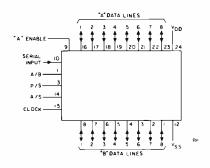

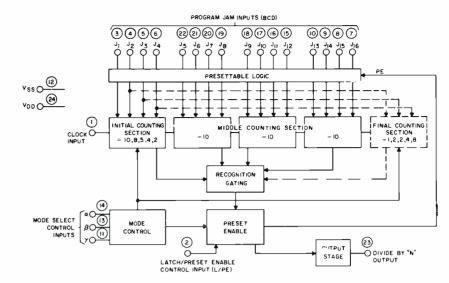

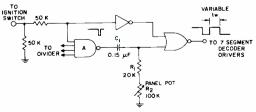

Fig. 1—A general purpose counter/latch/decoder/liquid-crystal-display driver system.

Fig. 2—Functional diagram of a liquid-crystal-display rate indicator.

THE RCA LINE OF COS/MOS standard parts has grown to include 50 commercially announced types with some 20 additional types to be announced over the next quarter. An expanding list of gate, flip-flop, counter, register, and general-purpose subsystem functions make up these 70 types. The availability of standard-part, staticlogic, cos/mos building blocks that operate from a single power supply and that are characterized by  $V_{pp}$ -to-GND (1-and-0) signal swings, wide operating-voltage (3 to 15V) and temperature (-55 to +125°C) ranges, high noise immunity (30% of  $V_{DD}$ ), low dissipation (5 µW typical per MSI package), and high input/low output impedances make cos/mos circuits ideal for the breadboarding and evaluation of complex system functions. In the final system implementation, such breadboards may serve as the production prototype from which only packaging and form factor are changed or as the basis on which single or multiple cos/mos custom chips are designed. Many systems, in fact, are finally implemented using a mixture of custom-designed and standard parts. Table I categorizes the available standard parts and indicates major operational characteristics. The contents of the table underscore the capability of the RCA cos/mos CD4000A line. With cos/Mos, breadboarding, evaluation, and modification of prototype systems before commitment to a final design has become an economic and practical reality. The breadboard circuits act as ideal supplements to computer simulation of dynamic criteria, such as critical speed paths.

### Sample subsystem applications

The CD4000A series of standard cos/ mos parts is described in detail in the CD4000A data sheets.<sup>3</sup> Summary information is presented in the quick-reference guides.<sup>4</sup> As a means of illustrating the flexibility of the CD4000A series, a set of sample applications are given below. These samples are not aimed at a particular system use; they do, however, highlight unique features of some of the individual parts and demonstrate overall capability of the combined cos/mos line.

Fig. 1 illustrates a general purpose

Reprint RE-18-4-17 (ST-6127)

Final manuscript received October 6, 1972.

Table I—COS/MOS "A" series standard-parts family (3- to 15-V operating-voltage range).

| Category          | Description                                                              | Pkg.                 | Performance/<br>comments_                                                                                                   |

|-------------------|--------------------------------------------------------------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------|

| Basic building bl |                                                                          |                      |                                                                                                                             |

|                   | CD4007A—dual complementary pair                                          | 14 pin               | MOS device evaluation,<br>and basic breadboarding                                                                           |

|                   | and inverter<br>CD4016A—quad bidirectional switch                        | 14 pin               | Transmission gating,<br>analog switch                                                                                       |

| Gates             |                                                                          | V.                   |                                                                                                                             |

|                   | CD4001A-dual 3-input NOR +                                               | 14 pin 🚶             |                                                                                                                             |

|                   | Invertor<br>CD4001quad 2-input NOR                                       | 14 pin               |                                                                                                                             |

| NOR               | 1                                                                        | - 1                  |                                                                                                                             |

|                   | CD4002A—dual 4-input NOR<br>CD4025A—triple 3-input NOR                   | 14 pin<br>14 pin     |                                                                                                                             |

|                   |                                                                          |                      | Micropower quiescent                                                                                                        |

|                   |                                                                          | 7                    | dissipation0.01 μW<br>(typ.) at 10V                                                                                         |

|                   | CD4011A-quad 2-input NAND                                                | 14 pin /             | Medium speeds—25ns                                                                                                          |

| NAND              | CD4012A—dual 4-input NAND<br>CD4023A—triple 3-input NAND                 | 14 pin<br>14 pin     | (typ.) at 10V, 15pF<br>loads                                                                                                |

|                   | CD4019A—quad AND-OR select gate<br>CD4037A—triple AND-OR bi-phase        | 16 pin               | rougs                                                                                                                       |

| Other             | CD4037A—triple AND-OR bi-phase pairs                                     | 14 pin               |                                                                                                                             |

| Ottier            | CD4048A—multifunction expandable                                         | 16 pin               |                                                                                                                             |

|                   | 8-input gate<br>CD4030A—quad exclusive OR gate                           | 14 pin /             |                                                                                                                             |

|                   | ···                                                                      | TV Prot (to)         |                                                                                                                             |

| Buffers/level con | CD4009A-hex buffer/converter-                                            | 16 pin )             | COS/MOS—TTI.                                                                                                                |

|                   | inverting                                                                | }                    | level conversion, 2TTL                                                                                                      |

|                   | CD4010A—hex buffer/converter-<br>non inverting                           | 16 pin )             | load drive                                                                                                                  |

|                   | CD4049A-hex buffer/converter-                                            | l6 pin )             | Similar to CD4009A/                                                                                                         |

|                   | inverting<br>CD4050A—hex buffer/converter-<br>non inverting              | 16 pin \$            | 10A with-single supply<br>No supply sequencing<br>requirements                                                              |

|                   | CD4041A—quad true/complement huffer                                      | 14 pin               | 2TTL load drive high<br>source- & sink-current<br>capability                                                                |

| Flip-flops/latche | s/monostable-astable multivibrators                                      |                      |                                                                                                                             |

|                   | CD4013A-dual "D" flip flop with                                          | 14 pin )             | Toggle freq. is 8MHz                                                                                                        |

| Clocked-master    | Set/reset<br>CD4027A—dual IK flip-flop with                              | 16 pin \$            | (typ.) at IOV, 15 plf<br>loads                                                                                              |

|                   | set/reset                                                                |                      | 10000                                                                                                                       |

| l.atch            | CD4042A—quad clucked "D" latch<br>CD4043A—quad 3-state NOR R/S latch     | 16 pin }<br>16 pin } | 3-state output capability                                                                                                   |

| 1.6.67            | CD4044A—Quad 3-state NAND R/S                                            | 16 pin )             | 3 state output capacitity                                                                                                   |

| Monostable/       | latch<br>CD4047A—low-power monstable/astable                             | 14 pin               | Astable-Dissipation =                                                                                                       |

| ustable           | multivibrator                                                            | .,                   | 500μW (typ.) at f=<br>5kHz, 5 volts<br>Astable/Monostable—<br><55% variation in time<br>periods within oper-<br>ating range |

| Registers         |                                                                          |                      |                                                                                                                             |

| (                 | CD4015A—dual 4-stage serial                                              | 16 pin               |                                                                                                                             |

|                   | in/parallel out<br>CD4014A—8-stage synchronous<br>parallel in/serial out | l6 pin               |                                                                                                                             |

| ,                 | C D4021A—8-stage asynchronous<br>parallel in/serial out                  | I6 pin               |                                                                                                                             |

|                   | CD4034A8-stage bidirectional parallel/                                   | 24 pin               | Enable control                                                                                                              |

| tatic (           | serial "D" input/output bus                                              |                      | Bidirectional signal                                                                                                        |

|                   | register CD4035A-4-stage parallel in/parallel out shift register         | 16 pin               | capability<br>IK serial input                                                                                               |

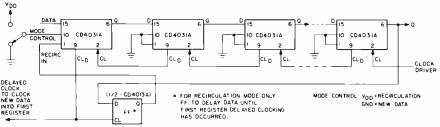

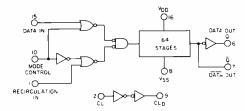

|                   | CD4006A-18-stage static shift register                                   | 14 pin               | 4 or 5 stage sections                                                                                                       |

| (                 | CD4031A-64-stage static shift register                                   | 16 pin               | Recirculation, delayed clock                                                                                                |

|                   | TA5956A-200-stage dynamic shift<br>register (developmental)              | l6 pin               | 1-phase or 2-phase<br>clocking                                                                                              |

| Iline addressing TA5352—256-word by 1-bit random-access NDRO memory with 3-state outputs (developmental)  Arithmetic functions  CD4008A—4-bit full adder CD4032A—triple serial adder-positive logic CD40038A—triple serial adder negative logic CD4005A—bit arithmetic array  CD4005A—bit arithmetic array  COunters  Ripple CD4005A—bit arithmetic array  CD4005A—bit arithmetic array  COunters  CD4005A—21-stage hinary counter CD4005A—10 decade counter/divider + 16 pin CD4005A—10 decade counter/divider + 16 pin CD4005A—10 decade counter divider + 16 pin CD405A—10 decade counter divider + 16 pin Fixed or programmable divide-by-2 through 10 CD405A—10 decade counter/divider + 16 pin Fixed or programmable divide-by-2 through 10 CD405A—21-stage hinary counter CD4005A—10 decade counter/divider + 16 pin Fixed or programmable divide-by-2 through 10 CD405A—21-stage hinary counter CD4005A—10 decade counter/divider + 16 pin Fixed or programmable divide-by-2 through 10 CD405A—21-stage hinary counter CD405A—4 decade counter/divider + 16 pin Fixed or programmable divide-by-2 through 10 CD405A—4 decade counter/divider + 16 pin Fixed or programmable divide-by-2 through 10 CD405A—4 decade counter/divider + 16 pin Fixed or programmable divide-by-3 counter CD405A—4 decade counter/divider + 16 pin Fixed or programmable divide-by-3 counter CD405A—4 decade counter/divider + 16 pin Fixed or programmable divide-by-3 counter CD405A—4 decade counter/divider + 16 pin Fixed or programmable divide-by-3 counter CD405A—4 decade counter/divider + 16 pin Fixed or programmable divide-by-3 counter CD405A—5 decade counter/divider + 16 pin Fixed or programmable divide-by-3 counter CD405A—5 decade counter/divider + | Category                     | Description                                                                                        | Pkg.             | Performance/<br>comments                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|----------------------------------------------------------------------------------------------------|------------------|---------------------------------------------------|

| access NDRO memory-binary addressing CD4039—4-word by 8-bit random access NDRO memory-direct word a content of the content of  | Memories                     |                                                                                                    |                  |                                                   |

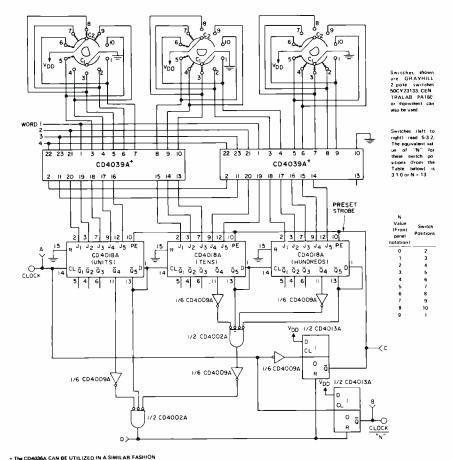

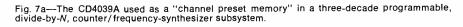

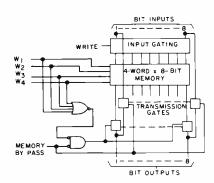

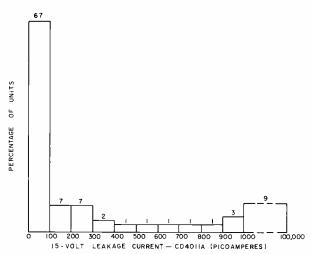

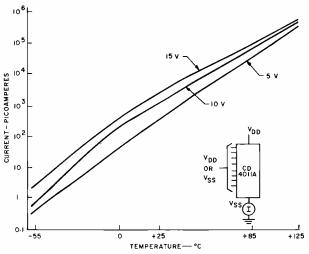

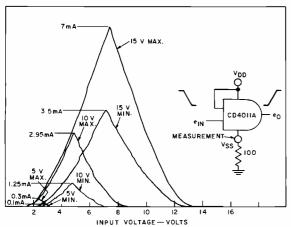

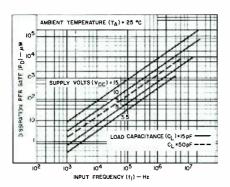

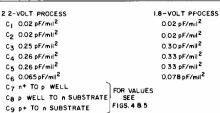

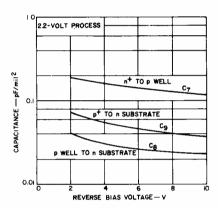

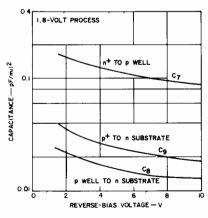

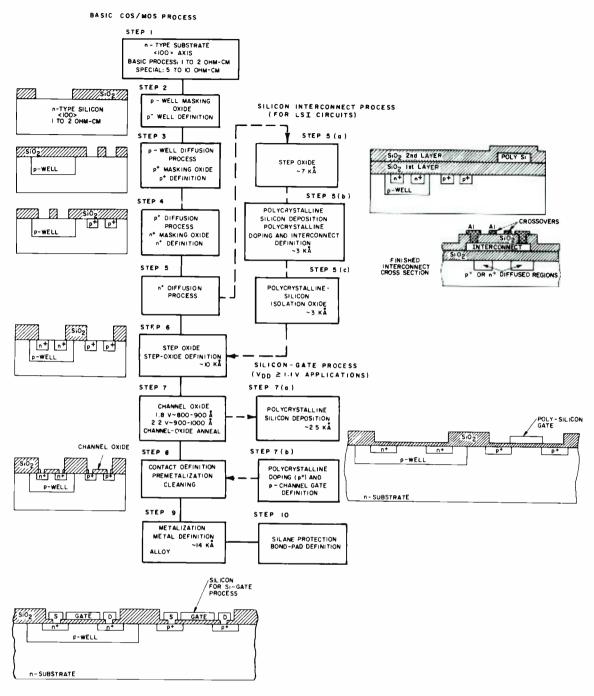

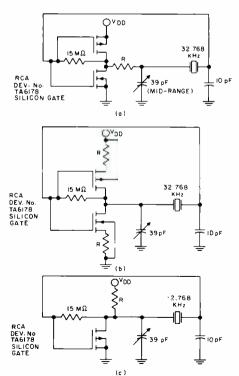

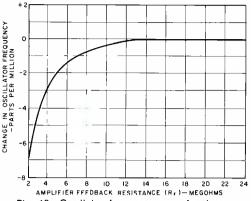

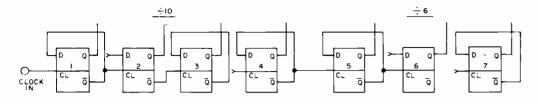

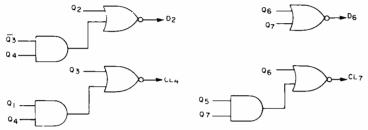

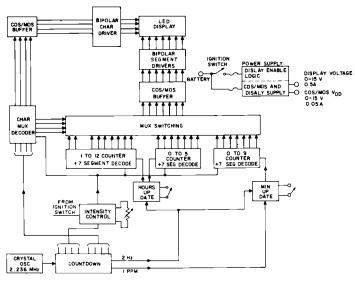

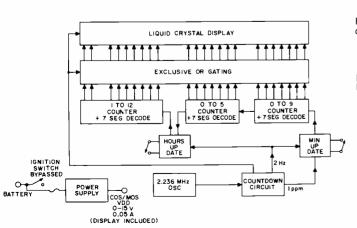

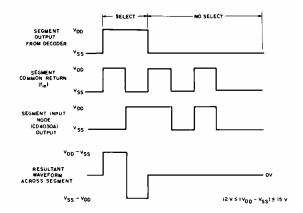

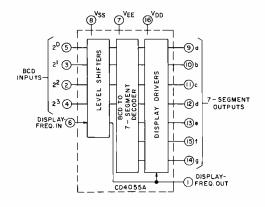

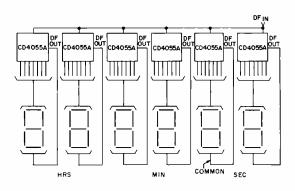

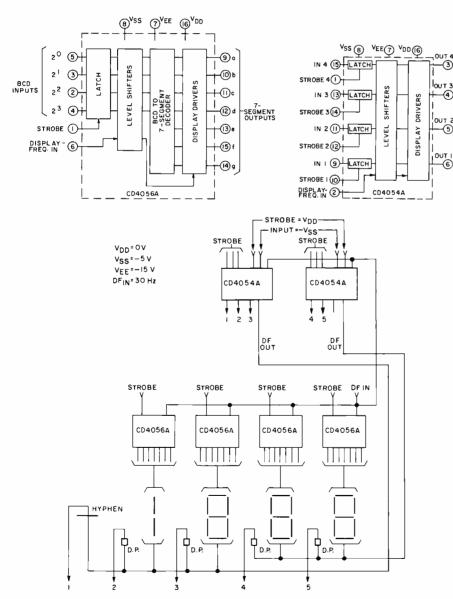

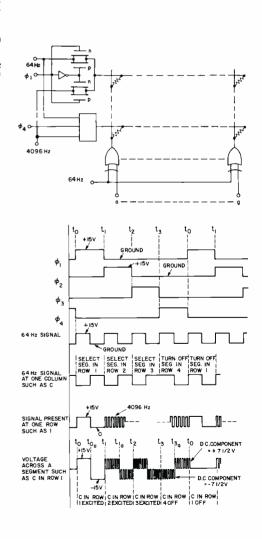

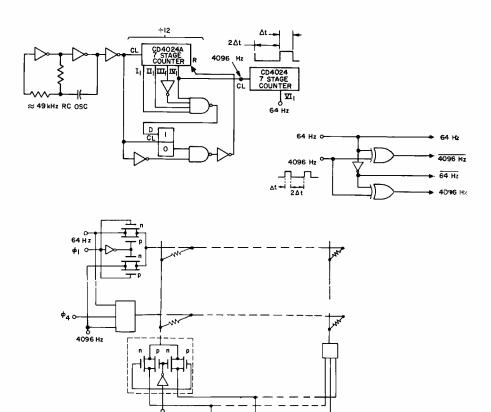

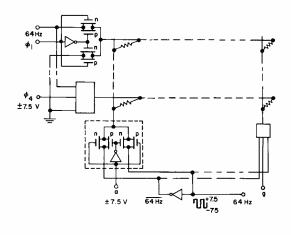

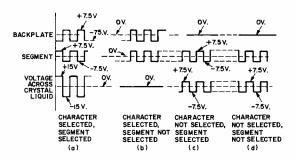

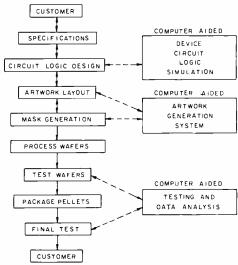

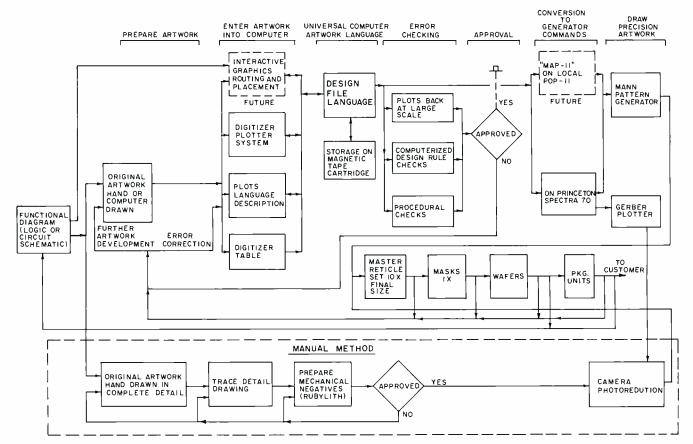

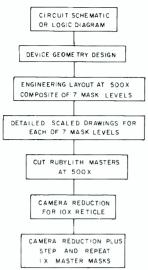

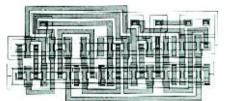

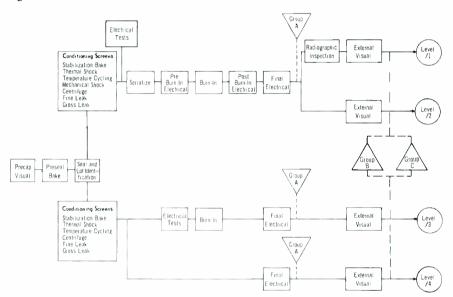

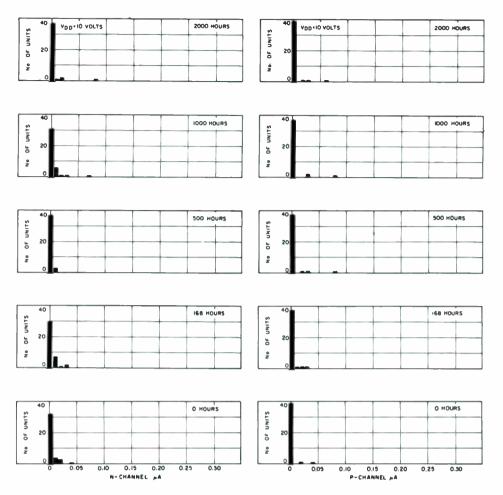

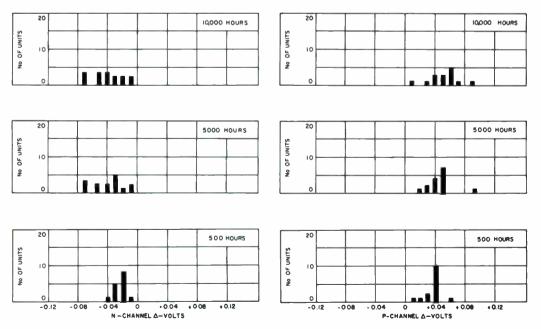

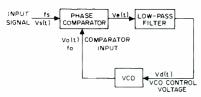

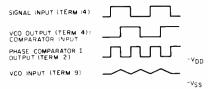

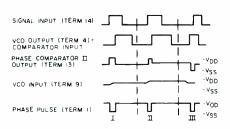

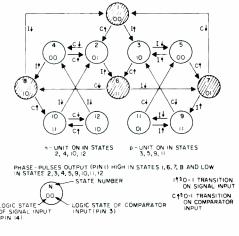

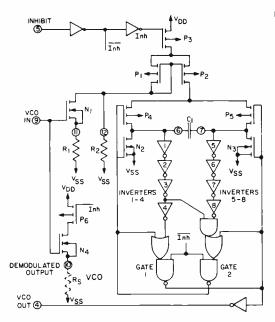

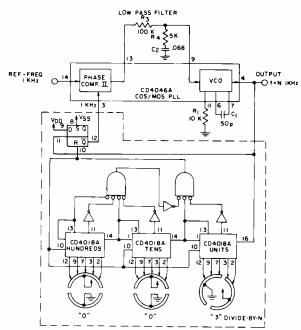

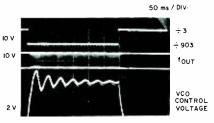

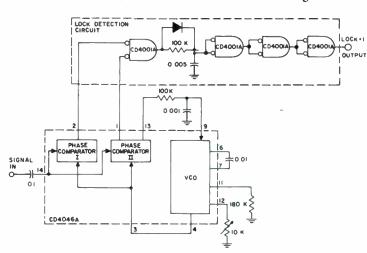

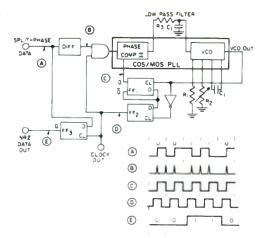

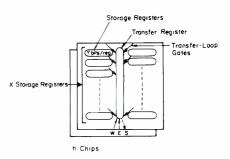

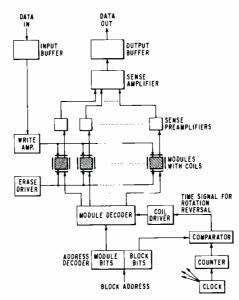

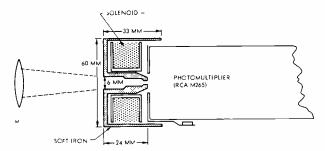

| access NDRO memory-direct word line addressing TA6335—256-word by 1-bit random-access NDRO memory with 3-state outputs (developmental)  Arithmetic functions  CD4008A—4-bit full adder CD4032A—triple serial adder-positive logic CD4038A—triple serial adder-positive logic CD4038A—triple serial adder negative logic logic CD4038A—triple serial adder negative logic logic CD4038A—triple serial adder negative logic logic CD403A—bit arithmetic array 28 pin Register on-chip 4-bit la-instruction capability—arithmetic/logical/ count/shift  Counters  Ripple CD4045A—21-stage binary counter logic   |                              | access NDRO memory-binary addressing                                                               | 1                |                                                   |